# FAILURE MECHANISM BASED STRESS TEST QUALIFICATION FOR DISCRETE SEMICONDUCTORS IN AUTOMOTIVE APPLICATIONS

**Component Technical Committee**

#### **TABLE OF CONTENTS**

# AEC-Q101 <u>Failure Mechanism Based</u> Stress Test Qualification for Discrete Semiconductors <u>in Automotive Applications</u>

Appendix 1: Definition of a Qualification Family

Appendix 2: Q101 Certification of Design, Construction and Qualification

Appendix 3: Qualification Plan

Appendix 4: Data Presentation Format

Appendix 5: Minimum Parametric Test Requirements

Appendix 6: Plastic Package Opening for Wire Bond Testing and Inspection

Appendix 7: Guideline on Relationship of Robustness Validation to AEC-Q101

#### **Attachments**

AEC-Q101-001: Electrostatic Discharge Test - Human Body Model

AEC-Q101-002: Electrostatic Discharge Test - Machine Model (DECOMMISSIONED)

AEC-Q101-003: Wire Bond Shear Test

AEC-Q101-004: Miscellaneous Test Methods

AEC-Q101-005: Electrostatic Discharge Test – <u>Charged Device</u> Model

AEC-Q101-006: Short Circuit Reliability Characterization of Smart Power Devices for 12V

<u>Systems</u>

**Component Technical Committee**

#### **Acknowledgment**

Any document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:

#### **Sustaining Members:**

Rick Forster Continental Corporation

Mark A. Kelly Delphi Corporation

Drew Hoffman Gentex Corporation

Steve Sibrel Harman

Gary Fisher Johnson Controls Eric Honosowetz Lear Corporation

#### **Technical Members:**

James Molyneaux Analog Devices

Joe Fazio Fairchild Semiconductor

Nick Lycoudes Freescale Werner Kanert Infineon

Scott Daniels International Rectifier

Mike Buzinski Microchip

Bob Knoell NXP Semiconductors

Zhongning Liang NXP Semiconductors

Mark Gabrielle ON Semiconductor

Tom Siegel Renesas Technology

Tony Walsh Renesas Technology

Bassel Atallah STMicroelectronics

Arthur Chiang Vishay Ted Krueger [Q101 Team Leader] Vishay

#### **Other Contributors**:

John Schlais

John Schlais

Continental Corporation

Continental Corporation

Continental Corporation

International Rectifier

Rene Rongen

Rene Rongen

Thomas Hough

Renesas Technology

Renesas Technology

This document is dedicated in memoriam to: Ted Krueger (1955-2013) Mark Gabrielle (1957-2013)

**Component Technical Committee**

#### NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.

AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.

AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in Conformance with this document shall be made unless all requirements stated in the document are met.

Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link http://www.aecouncil.com.

Published by the Automotive Electronics Council.

This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

Printed in the U.S.A. All rights reserved

Copyright © 2013 by the Sustaining Members of the Automotive Electronics Council. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.

**Component Technical Committee**

# FAILURE MECHANISM BASED STRESS TEST QUALIFICATION FOR DISCRETE SEMICONDUCTORS IN AUTOMOTIVE APPLICATIONS

Text enhancements and differences made since the last revision of this document are shown as underlined areas. Several figures and tables have also been revised, but changes to these areas have not been underlined.

<u>Unless otherwise stated herein, the date of implementation of this standard for new qualifications and re-qualifications is as of the publish date above.</u>

#### 1. SCOPE

This document defines minimum stress test driven qualification requirements and references test conditions for qualification of discrete semiconductors (e.g. transistors, diodes, etc.). This document does not relieve the supplier of their responsibility to meet their own company's internal qualification program. Additionally, this document does not relieve the supplier from meeting any user requirements outside the scope of this document. In this document, "user" is defined as any company developing or using a discrete semiconductor part in production. The user is responsible to confirm and validate all qualification and assessment data that substantiates conformance to this document.

#### 1.1 Purpose

The purpose of this specification is to determine that a <u>part</u> is capable of passing the specified stress tests and thus can be expected to give a certain level of quality / reliability in the application.

#### 1.2 Reference Documents

Current revision of the referenced documents will be in effect at the date of agreement to the qualification plan. Subsequent qualification plans will automatically use updated revisions of these referenced documents.

#### 1.2.1 Military

MIL-STD-750 Test Methods for Semiconductor Devices

#### 1.2.2 Industrial

UL-STD-94 Test for Flammability of Plastic Materials of Parts in Devices and Appliances.

JEDEC JESD-22 Reliability Test Methods for Packaged Devices

J-STD-002 Solderability Tests for Component Leads, Terminations, Lugs, Terminals and Wires.

J-STD-020 Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices

JESD22-A113 Preconditioning of Nonhermetic Surface Mount Devices Prior to Reliability Testing J-STD-035 Acoustic Microscopy for Nonhermetic Encapsulated Electronic Components

#### 1.2.3 Automotive

AEC-Q001 Guidelines for Part Average Testing

<u>AEC-Q005 Pb-Free Test Requirements</u>

AEC-Q101-001 ESD (Human Body Model)

AEC-Q101-003 Discrete Component Wirebond Shear Test

**Component Technical Committee**

AEC-Q101-004 Miscellaneous Test Methods

- Unclamped Inductive Switching

- Dielectric Integrity

- Destructive Physical Analysis

AEC-Q101-005 ESD (Charged Device Model)

AEC-Q101-006 Short Circuit Reliability Characterization of Smart Power Devices for 12V Systems

#### 1.2.4 Other

QS-9000 ISO-TS-16949

#### 1.2.5 Decommissioned

#### AEC-Q101-002 ESD Machine Model

• Removed from JEDEC due to obsolescence. HBM and CDM cover virtually all known ESD-related failure mechanisms.

#### 1.3 Definitions

#### 1.3.1 AEC Q101 Qualification

Successful completion and documentation of the test results from requirements outlined in this document allows the supplier to claim that the part is "AEC-Q101 qualified". The supplier, in agreement with the user, can perform qualification at sample sizes and conditions less stringent than what this document requires. However, that part cannot be considered "AEC-Q101 qualified" until such time that the unfulfilled requirements have been successfully completed. For ESD, it is highly recommended that the passing voltage be specified in the supplier datasheet with a footnote on any pin exceptions. This will allow suppliers to state, e.g., "AEC-Q101 qualified to ESD H1B", implying that supplier passes all AEC tests except the ESD level. Note that there are no "certifications" for AEC-Q101 qualification and there is no certification board run by AEC to qualify parts.

The minimum temperature range for discrete semiconductors per this specification shall be -40°C to +125°C operational, the minimum range for all LEDs shall be -40°C to +85°C operational. (Note: Some parts may be derated to zero at the maximum temperature.)

#### 1.3.2 Approval for Use in an Application

"Approval" is defined as user approval for use of a part in their application. The user's method of approval is beyond the scope of this document.

#### 1.3.3 Terminology

In this document, "part" refers to the same entity as would "device" or "component", that is, a singulated diode, transistor, varistor, etc. with the die molded in a plastic mold compound with metal leads for board attachment.

**Component Technical Committee**

#### 2. GENERAL REQUIREMENTS

#### 2.1 Precedence of Requirements

In the event of conflict in the requirements of this specification and those of any other documents, the following order of precedence applies:

- <u>a</u>. The purchase order

- <u>b</u>. The individual <u>agreed upon part</u> specification

- <u>c</u>. This document

- d. The reference documents in Section 1.2 of this document

- <u>e</u>. The supplier's data sheet

For the <u>part</u> to be considered qualified per this specification, the purchase order and/or individual <u>part</u> specification cannot waive or detract from the requirements of this document.

#### 2.2 The Use of Generic Data to Satisfy Qualification and Re-qualification Requirements

The use of generic (family) data to simplify the qualification/re-qualification process is encouraged. To be considered, the generic data must be based on the following criteria:

- <u>a.</u> Part qualification requirements listed in Table 2.

- <u>b</u>. <u>Matrix of specific requirements associated with each characteristic of the <u>part</u> and manufacturing process as shown in Table 3.</u>

- c. Definition of family guidelines established in Appendix 1.

- d. Represent a random sample of the normal population.

Appendix 1 defines the criteria by which <u>parts</u> are grouped into a qualification family for the purpose of considering the data from all family members to be equal and generically acceptable to the qualification of the <u>part</u> in question.

With proper attention to these qualification family guidelines, information applicable to other <u>parts</u> in the family can be accumulated. This information can be used to demonstrate generic reliability of a <u>part</u> family and minimize the need for <u>part</u>-specific qualification test programs. This can be achieved through qualification of a range of <u>parts</u> representing the "four corners" of the qualification family (e.g., highest/lowest voltage, largest/smallest die, etc.). Sources of generic data should come from supplier-certified test labs, and can include internal supplier's qualifications, user-specific qualifications and supplier's in-process monitors. The generic data to be submitted must meet or exceed the test conditions specified in Table 2. Table 1 provides guidelines showing how the available part test data may be applied to reducing the number of lots required for qualification. Electrical characterization to the individual user <u>part</u> specification must be performed for each <u>part</u> submission, generic characterization data is not allowed. The user(s) will be the final authority on the acceptance of generic data in lieu of specific part test data.

**Component Technical Committee**

Table 1: Part Qualification/Re-qualification Lot Requirements

| Part Information                                                                                                                        | Lot Requirements for Qualification                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| New part, no applicable generic data.                                                                                                   | Lot and sample size requirements per Table 2.                                                                                                |

| A part in a family is qualified. The part to be qualified is less complex and meets the Family Qualification Definition per Appendix 1. | Only <u>part</u> specific tests as defined in section 4.2 are required. Lot and sample size requirements per Table 2 for the required tests. |

| A new part that has some applicable generic data.                                                                                       | Review Appendix 1 to determine required tests from Table 2. Lot and sample sizes per Table 2 for the required tests.                         |

| Part process change.                                                                                                                    | Review Table 3 to determine which tests from Table 2 should be considered. Lot and sample sizes per Table 2 for the required tests.          |

Table 2 defines a set of qualification tests that must be considered for both new <u>part</u> qualifications and re-qualification associated with a design or process change.

Table 3 defines a matrix of appropriate qualification tests that must be considered for any changes proposed for the <u>part</u>. Table 3 is the same for both new processes and requalification associated with a process change. This table is a superset of tests that the supplier and user should use as a baseline for discussion of tests that are required for the qualification/requalification in question. It is the supplier's responsibility to present and document rationale for why any of the highlighted tests need not be performed.

#### 2.4 Test Samples

#### 2.4.1 Lot Requirements

Lot requirements are designated in Table 2, herein.

#### 2.4.2 Production Requirements

All qualification parts shall be produced on tooling and processes at the manufacturing site that will be used to support part deliveries at projected production volumes.

#### 2.4.3 Reusability of Test Samples

<u>Parts</u> that have been used for nondestructive qualification tests may be used to populate other qualification tests. <u>Parts</u> that have been used for destructive qualification tests may not be used any further except for engineering analysis.

**Component Technical Committee**

#### 2.4.4 Sample Size Requirements

Sample sizes used for qualification testing and/or generic data submission must be consistent with the specified minimum sample sizes and acceptance criteria in Table 2. If the supplier elects to submit generic data for qualification/requalification, the specific test conditions and results must be reported. Existing applicable generic data should first be used to satisfy these requirements and those of Section 2.3 for each test requirement in Table 2. Part specific qualification testing should be performed if the generic data does not satisfy these requirements.

• The supplier must perform any combination of the specific part to be qualified and/or an acceptable generic part(s) that totals a minimum of 3 lots x 77 pcs/lot.

#### 2.4.5 Time Limit for Acceptance of Generic Data

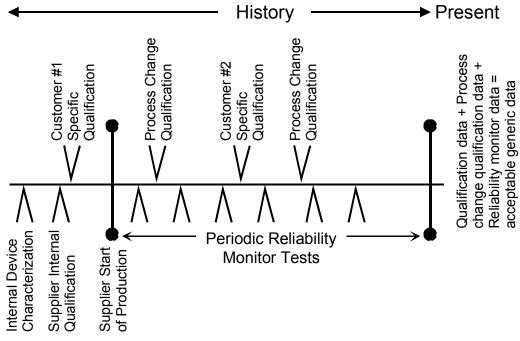

There are no time limits for the acceptability of generic data as long as the appropriate reliability data is submitted to the user for evaluation. Use the diagram below for appropriate sources of reliability data that can be used. This data must come from the specific part or a part in the same qualification family, as defined in Appendix 1. Potential sources of data could include any customer specific data (withhold customer name), process change qualification, and periodic reliability monitor data (see Figure 1).

**Note:** Some process changes (e.g., die shrink) will affect the use of generic data such that data obtained before these types of changes will not be acceptable for use as generic data.

Figure 1: Generic Data Time Line

#### 2.4.6 Pre- and Post-Stress Test Requirements

All pre- and post-stress test parts must be tested to the electrical characteristics defined in the individual user part detail specification at room temperature.

**Component Technical Committee**

#### 2.5 Definition of Test Failure after Stressing

Test failures are defined as devices exhibiting any of the following criteria:

- <u>a.</u> Parts not meeting the electrical test limits defined in the first user's <u>part</u> specification or appropriate supplier generic <u>part</u> specification. Minimum test parametric requirements shall be as specified in Appendix 5.

- <u>b.</u> Parts not remaining within ± 20% of the initial reading of each test (with the exception of leakage limits which are not to exceed 10 times the initial value for moisture tests and 5 times the initial value for all others) after completion of environmental testing. Parts exceeding these guidelines must be justified by the supplier and approved by the user. For leakages below 100nA, tester accuracy may prevent a post stress analysis to initial reading.

- c. Any part exhibiting external physical damage attributable to the environmental test.

If the cause of failure is agreed (by the manufacturer and the user) to be due to mishandling or ESD, the failure shall be discounted, but reported as part of the data submission.

#### 2.6 Criteria for Passing Qualification/Re-qualification

Passing all appropriate qualification tests specified in Table 1, either by performing the tests (acceptance of zero failures using the specified minimum sample size) on the specific part or demonstrating acceptable family generic data (using the family definition guidelines defined in Appendix 1 and the total required lot and sample sizes), qualifies the <u>part</u> per this document.

<u>Parts</u> that have failed the acceptance criteria of tests required by this document require the supplier to satisfactorily determine root cause and corrective action to assure the user that the failure mechanism is understood and contained. The <u>part</u> shall not be considered as passing stress-test qualification until the root cause of the failure is determined and the corrective and preventive actions are confirmed to be effective. New samples or data may be requested to verify the corrective action. If generic data contains any failures, the data is not usable as generic data unless the supplier has documented corrective action or containment for the failure condition.

Any unique reliability tests or conditions requested by the user and not specified in this document shall be agreed upon between the supplier and user requesting the test, and will not preclude a device from passing stress-test qualification as defined by this document.

#### 2.7 Alternative Testing Requirements

Any deviation from the test requirements and conditions listed in Table 2 are beyond the scope of this document. Deviations (e.g., accelerated test methods) must be demonstrated to the AEC for consideration and inclusion into future revisions of this document.

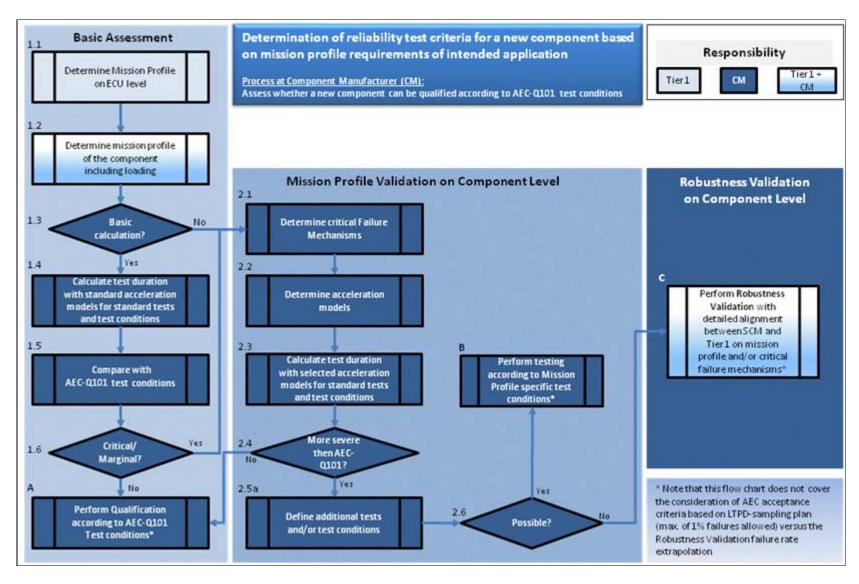

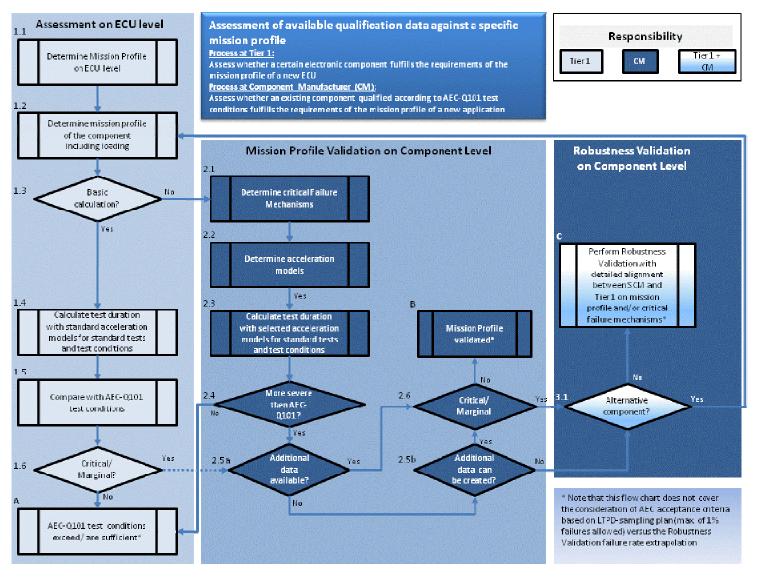

<u>See Appendix 7: Guideline on Relationship of Robustness Validation to AEC-Q101 for more information.</u>

#### 3. QUALIFICATION AND REQUALIFICATION

#### 3.1 Qualification of a New Part

Stress test requirements and corresponding test conditions for a new <u>part</u> qualification are listed in Table 2. For each qualification, the supplier must present data for ALL of these tests, whether it is stress test results on the specific <u>part</u> or acceptable generic family data. A review is to be made of

**Component Technical Committee**

other parts in the same generic family to ensure that there are no common failure mechanisms in that family. Justification for the use of generic data, whenever it is used, must be demonstrated by the supplier and approved by the user. For each part qualification, the supplier must present Certificate of Design, Construction and Qualification to the requesting user. See Appendix 2.

#### 3.2 Re-qualification of a Changed Part

Re-qualification of a part is required when the supplier makes a change to the product and/or process that impacts (or could potentially impact) the form, fit, function, quality and/or reliability of the part (see Table 3 for guidelines).

#### 3.2.1 Process Change Notification

The supplier will meet <u>mutually agreed upon</u> requirements for product/process changes.

#### 3.2.2 Changes Requiring Re-qualification

As a minimum, any change to the product, as defined above, requires performing the applicable tests listed in Table 2, using Table 3 to determine the re-qualification test plan. Table 3 should be used as a guide for determining which tests need to be performed or whether equivalent generic data can be submitted for the test(s).

#### 3.2.3 Criteria for Passing Re-qualification

All requalification failures shall be analyzed for root cause, with corrective and preventive actions established as required. The part and/or qualification family may be granted "qualification status" if, as a minimum, proper containment is demonstrated and approved by the user, until corrective and preventative actions are in place.

#### 3.2.4 User Approval

A change may not affect a part's operating temperature grade, but may affect its performance in an application. Individual user authorization of a process change shall be based on a contract between Supplier and User, and is outside the scope of this document.

#### 3.3 Qualification Test Plan

The supplier is requested to initiate a discussion with each user (as needed) resulting in completion of a signed Qualification Test Plan agreement as soon as possible after supplier selection for new parts, and at the time of notification (see Section 3.2.2) prior to process changes. The Qualification Test Plan, as defined in Appendix 3, shall be used to provide a consistent method of documentation supporting what testing will be performed as required by Tables 2 & 3.

#### 4 QUALIFICATION TESTS

#### 4.1 General Tests

Test details are given in Table 2. Not all tests apply to all <u>parts</u>. For example, certain tests apply only to hermetically packaged <u>parts</u>, others apply only to power MOSFET <u>parts</u>, and so on. The applicable tests for the particular <u>part</u> type are indicated in the "Note" column and the "Additional Requirements" column of Table 2. The "Additional Requirements" column of Table 2 also serves to highlight test requirements that supersede those described in the referenced test.

**Component Technical Committee**

#### 4.2 Part Specific Tests

The following tests must be performed on the specific <u>part</u> (i.e., family data is not allowed for these tests):

- a. Electrostatic Discharge Characterization (Table 2, Test #11)

- <u>b</u>. Parametric Verification (Table 2, Test #4) The supplier must demonstrate that the part is capable of meeting parametric limits detailed in the individual user part specification.

#### 4.3 Data Submittal Type

Data to be submitted to the user are classified in three types (Data Type column in Table 2):

#### 4.3.1 Data Type 1

Data (generic or specific) from these tests should be formatted as defined in Section 4.4 and included in each qualification submission.

#### 4.3.2 Data Type 2

Package specific data that should not be included with each qualification submission (except where the package is new). In place of this data the supplier can submit a "Document of Completion" that references successful completion of the specific test previously performed, provided no significant changes have been made. For Test #14 (Physical Dimensions), the Document of Completion should be completed referencing the appropriate user packaging specification.

#### 4.3.3 Data Type 3

Re-qualification data should be included in the qualification submission as required by Table 3. These tests shall be considered by the supplier during re-qualification plan development as useful tools to provide supporting rationale for new part qualification (including new packages) and/or process changes. It is the supplier's responsibility to present rationale for why any of these tests need not be performed.

#### 4.4 Data Submission Format

A data summary shall be submitted as defined in Appendix 4. Raw data and histograms shall be submitted to the individual user upon request. All data and documents (e.g., justification for non-performed tests, etc.) shall be maintained by the supplier in accordance with QS-9000 and/or TS-16949 requirements.

#### 4.5 Requirements for Testing Pb-free Components

The supplier shall follow the requirements of AEC-Q005 Pb-Free Test Requirements for all parts whose plating material on the leads/terminations contains <1000ppm by weight of lead (Pb).

|           | TABLE 2 - QUALIFICATION TEST DEFINITIONS    |             |              |                                      |                                             |                                                                                 |                          |                                                                     |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-----------|---------------------------------------------|-------------|--------------|--------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| #         | Stress                                      | Abrv        | Data<br>Type | Note                                 | Sample<br>Size<br>per Lot                   | # of<br>Lots                                                                    | Accept<br>on #<br>Failed | Reference<br>(current<br>revision)                                  | Additional Requirements                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 1         | Pre- and Post-<br>Stress Electrical<br>Test | TEST        | 1            | NG                                   | tested pe<br>requirement<br>appropriate     | ualification parts ested per the uirements of the propriate part specification. |                          | User<br>specification or<br>supplier's<br>standard<br>specification | Test is performed as specified in the applicable stress reference at room temperature.                                                                                                                                                                                                                                         |  |  |  |  |

| 2         | Pre-conditioning                            | PC          | 1            | GS                                   | SMD quali<br>parts <u>before</u><br>8, 9, & | Test # 7,                                                                       | 0                        | JESD22<br>A-113                                                     | Performed on surface mount <u>parts</u> (SMDs) prior to <u>Test # 7, 8, 9, &amp; 10</u> only. TEST before and after PC. Any replacement of parts must be reported.                                                                                                                                                             |  |  |  |  |

| 3         | External Visual                             | EV          | 1            | NG                                   | All qualificat submitted for                |                                                                                 | 0                        | JESD22<br>B-101                                                     | Inspect <u>part</u> construction, marking and workmanship.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 4         | Parametric<br>Verification                  | PV          | 1            | N                                    | 25                                          | 3<br>Note A                                                                     | 0                        | Individual AEC user specification                                   | Test all parameters according to user specification over the part temperature range to insure specification compliance.                                                                                                                                                                                                        |  |  |  |  |

| 5         | High Temperature<br>Reverse Bias            | HTRB        | 1            | <u>C</u> DG <u>K</u><br>UVP <u>X</u> | 77                                          | 3<br>Note B                                                                     | 0                        | MIL-STD-750-1<br>M1038 Method A                                     | 1000 hours at the maximum DC Reverse Voltage rated junction temperature specified in the user/supplier specification. The ambient temperature T <sub>A</sub> is to be adjusted to compensate for current leakage. TEST before and after HTRB as a minimum. (See note X HTRB.)  To be implemented on, or before, April 1, 2014. |  |  |  |  |

| <u>5a</u> | AC blocking voltage                         | ACBV        | <u>1</u>     | CDGU<br>PY                           | <u>77</u>                                   | 3<br>Note B                                                                     | <u>0</u>                 | MIL-STD-750-1<br>M1040 Test<br>condition A                          | 1000 hours at the maximum AC blocking voltage and junction temperature specified in the user/supplier specification. The ambient temperature T <sub>A</sub> is to be adjusted to compensate for current leakage. TEST before and after ACBV as a minimum.                                                                      |  |  |  |  |

| <u>5b</u> | High Temperature<br>Forward Bias            | <u>HTFB</u> | <u>1</u>     | DGUZ                                 | <u>77</u>                                   | 3<br>Note B                                                                     | <u>0</u>                 | <u>JESD22</u><br><u>A-108</u>                                       | 1000 hours at the maximum forward bias. TEST before and after HTFB as a minimum.                                                                                                                                                                                                                                               |  |  |  |  |

| <u>5c</u> | Steady State<br>Operational                 | <u>SSOP</u> | 1            | CDGU<br>O                            | <u>77</u>                                   | 3<br>Note B                                                                     | <u>0</u>                 | MIL-STD-750-1<br>M1038 Condition<br>B (Zeners)                      | 1000 hours at rated IZ max, T <sub>A</sub> to rated T <sub>J</sub> , TEST before and after SSOP as a minimum.                                                                                                                                                                                                                  |  |  |  |  |

|                        | TABLE 2 - QUALIFICATION TEST DEFINITIONS (Continued) |             |              |                    |                           |              |                          |                                                    |                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------|------------------------------------------------------|-------------|--------------|--------------------|---------------------------|--------------|--------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| #                      | Stress                                               | Abrv        | Data<br>Type | Note               | Sample<br>Size<br>per Lot | # of<br>Lots | Accept<br>on #<br>Failed | Reference<br>(current<br>revision)                 | Additional Requirements                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6                      | High Temperature<br>Gate Bias                        | HTGB        | 1            | <u>C</u> DG<br>MUP | 77                        | 3<br>Note B  | 0                        | JESD22<br>A-108                                    | 1000 hours at the specified T <sub>J</sub> (max) rating, with gate biased at 100% of maximum gate voltage rating indicated in the detail specification with <u>part</u> biased OFF. Can reduce duration to 500 hours through increasing T <sub>J</sub> by 25°C <sub>1</sub> TEST before and after HTGB as a minimum.               |  |  |  |

| 7                      | Temperature<br>Cycling                               | TC          | 1            | DGU                | 77                        | 3<br>Note B  | 0                        | JESD22<br>A-104<br>Appendix 6                      | 1000 cycles ( $T_A$ = minimum range of -55°C to maximum rated junction temperature, not to exceed 150°C). Can reduce duration to 400 cycles using $T_A$ (max) = 25°C over part maximum rated junction temperature or using $T_A$ (max) = 175°C if the maximum rated junction temperature is above 150°C. TEST before and after TC. |  |  |  |

| <u>7a</u>              | Temperature Cycling Hot Test                         | <u>TCHT</u> | 1            | DGU1               | <u>77</u>                 | 3<br>Note B  | <u>0</u>                 | <u>JESD22</u><br><u>A-104</u><br><u>Appendix 6</u> | 125°C TEST after TC, followed by decap and wire pull on all wires from 5 devices per appendix 6 for parts with internal bond wire sizes 5 mil diameter and less. (Samples may be a sub set of test 7).  To be implemented on, or before, April 1, 2014.                                                                            |  |  |  |

| 7a<br>alt              | TC Delamination<br>Test                              | TCDT        | 1            | DGU1               | <u>77</u>                 | 3<br>Note B  | <u>0</u>                 | JESD22<br>A-104<br>Appendix 6<br>J-STD-035         | 100% C-SAM inspection after TC, followed by decap, inspection or wire pull on all wires from 5 parts per appendix 6 for 5 highest delaminated parts. If C-SAM shows no delaminating, no decap, inspection and wire pull is required.  To be implemented on, or before, April 1, 2014.                                              |  |  |  |

| <u>7b</u>              | Wire Bond Integrity                                  | <u>WBI</u>  | <u>3</u>     | DGUF               | <u>5</u>                  | 3<br>Note B  | <u>0</u>                 | MIL-STD-750<br>Method 2037                         | 500 hours, T <sub>A</sub> = maximum rated Tj for bonding of dissimilar metals (e.g., Au/Al), decap and wire pull/bond inspection after WBI on all wires from a maximum of 5 parts.  To be implemented on, or before, April 1, 2014.                                                                                                |  |  |  |

| 8                      | Unbiased Highly Accelerated Stress Test              | UHAST       | 1            | CDG<br>U           | <u>77</u>                 | 3<br>Note B  | <u>0</u>                 | <u>JESD22</u><br><u>A-118</u>                      | 96 hours at TA=130°C/85%RH. TEST before and after 96 hours UHAST.                                                                                                                                                                                                                                                                  |  |  |  |

| <u>8</u><br><u>alt</u> | Autoclave                                            | AC          | 1            | CDG<br>U           | 77                        | 3<br>Note B  | 0                        | JESD22<br>A-102                                    | 96 hours, TA = 121°C, RH = 100%, 15psig. TEST before and after AC.                                                                                                                                                                                                                                                                 |  |  |  |

|                 | TABLE 2 - QUALIFICATION TEST DEFINITIONS (Continued) |                    |                          |            |                                              |              |                          |                                          |                                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------|------------------------------------------------------|--------------------|--------------------------|------------|----------------------------------------------|--------------|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| #               | Stress                                               | Abrv               | Data<br>Type             | Note       | Sample<br>Size<br>per Lot                    | # of<br>Lots | Accept<br>on #<br>Failed | Reference<br>(current<br>revision)       | Additional Requirements                                                                                                                                                                                                                                                                                            |  |  |

| 9               | Highly Accelerated<br>Stress Test                    | HAST               | 1                        | CDG<br>UV  | 77                                           | 3<br>Note B  | 0                        | JESD22<br>A-110                          | 96 hours at $T_A$ =130°C/85%RH, or 264hrs TA=110°C /85%RH with part reverse bias at 80% of rated voltage up to a voltage above which arcing in the chamber will likely occur (typically 42V). TEST before and after HAST.                                                                                          |  |  |

| <u>9</u><br>alt | High Humidity<br>High Temp.<br>Reverse Bias          | H <sup>3</sup> TRB | 1                        | DGU<br>V   | 77                                           | 3<br>Note B  | 0                        | JESD22<br>A-101                          | 1000 hours at $T_A$ = 85°C/85% RH with <u>part</u> reverse biased at 80% of rated breakdown voltage up to a maximum of 100V or limit of chamber. TEST before and after H3TRB as a minimum.                                                                                                                         |  |  |

| <u>9a</u>       | High Temperature<br>High Humidity Bias               | <u>HTHHB</u>       | <u>1</u>                 | DGUZ       | <u>77</u>                                    | 3<br>Note B  | <u>0</u>                 | <u>JESD22</u><br><u>A-101</u>            | $1000 \text{ hours at } T_A = 85^{\circ}\text{C/85\% RH with part Forward}$<br>biased. TEST before and after H3TRB as a minimum.                                                                                                                                                                                   |  |  |

| 10              | Intermittent<br>Operational Life                     | IOL                | 1                        | DGTU<br>WP | 77                                           | 3<br>Note B  | 0                        | MIL-STD-750<br>Method 1037               | Tested per duration indicated in <u>Table 2A</u> . $T_A$ =25°C.<br><u>Parts</u> powered to insure $\Delta T_J \ge 100$ °C (not to exceed absolute maximum ratings). TEST before and after IOL as a minimum.                                                                                                        |  |  |

| 10<br>alt       | Power and<br>Temperature Cycle                       | PTC                | 1                        | DGTU<br>W  | 77                                           | 3<br>Note B  | 0                        | JESD22<br>A-105                          | Perform PTC if $\Delta T_J \geq 100^{\circ}$ C cannot be achieved with IOL. Tested per duration indicated for Timing Requirements in Table 2A. <u>Parts</u> powered and chamber cycled to insure $\Delta T_J \geq 100^{\circ}$ C (not to exceed absolute maximum ratings). TEST before and after PTC as a minimum. |  |  |

| 11              | ESD<br>Characterization                              | ESD                | 1<br>(HBM)<br>2<br>(CDM) | DW         | 30 <u>each</u><br><u>HBM /</u><br><u>CDM</u> | 1            | 0                        | AEC<br>Q101-001, and<br><u>Q101-</u> 005 | The supplier must document that the package could not hold sufficient charge to perform the test. TEST before and after ESD.                                                                                                                                                                                       |  |  |

| 12              | Destructive<br>Physical Analysis                     | DPA                | 1                        | DG         | 2                                            | 1<br>Note B  | 0                        | AEC-Q101-004<br>Section 4                | Random sample of <u>parts</u> that have successfully completed H3TRB or HAST, and TC.                                                                                                                                                                                                                              |  |  |

| 13              | Physical<br>Dimension                                | PD                 | 2                        | NG         | 30                                           | 1            | 0                        | JESD22<br>B-100                          | Verify physical dimensions to the applicable user part packaging specification for dimensions and tolerances.                                                                                                                                                                                                      |  |  |

| 14              | Terminal Strength                                    | TS                 | 2                        | DGL        | 30                                           | 1            | 0                        | MIL-STD-750<br>Method 2036               | Evaluate lead integrity of leaded <u>parts</u> only.                                                                                                                                                                                                                                                               |  |  |

| 15              | Resistance to Solvents                               | RTS                | 2                        | DG         | 30                                           | 1            | 0                        | JESD22<br>B-107                          | Verify marking permanency. (Not required for laser etched parts or parts with no marking.)                                                                                                                                                                                                                         |  |  |

|    | TABLE 2 - QUALIFICATION TEST DEFINITIONS (Continued) |      |              |            |                                              |                                                                                                                                                                                                                                                                                 |                          |                                                    |                                                                                                                                         |  |  |  |  |

|----|------------------------------------------------------|------|--------------|------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| #  | Stress                                               | Abrv | Data<br>Type | Note       | Sample<br>Size<br>per Lot                    | # of<br>Lots                                                                                                                                                                                                                                                                    | Accept<br>on #<br>Failed | Reference<br>(current<br>revision)                 | Additional Requirements                                                                                                                 |  |  |  |  |

| 16 | Constant<br>Acceleration                             | CA   | 2            | DGH<br>(1) | 30                                           | 1<br>Note B                                                                                                                                                                                                                                                                     | 0                        | MIL-STD-750<br>Method 2006                         | Y1 plane only, 15K g-force. TEST before and after CA.                                                                                   |  |  |  |  |

| 17 | Vibration Variable<br>Frequency                      | VVF  | 2            | DGH<br>(2) | sequential packages                          | Items 16 through 19 are sequential tests for hermetic packages. (See note H on Legend page.)  JESD22  B-103  Use a constant displacement of 0.06 inches amplitude) over the range of 20Hz to 100 H constant peak acceleration over the range of KHz. TEST before and after VVF. |                          |                                                    |                                                                                                                                         |  |  |  |  |

| 18 | Mechanical Shock                                     | MS   | 2            | DGH<br>(3) |                                              |                                                                                                                                                                                                                                                                                 | 0                        | JESD22<br>B-104                                    | 1500 g's for 0.5mS, 5 blows, 3 orientations. TEST before and after MS.                                                                  |  |  |  |  |

| 19 | Hermeticity                                          | HER  | 2            | DGH<br>(4) |                                              |                                                                                                                                                                                                                                                                                 | 0                        | JESD22<br>A-109                                    | Fine and Gross leak test per individual user specification.                                                                             |  |  |  |  |

| 20 | Resistance to<br>Solder Heat                         | RSH  | 2            | DG         | 30                                           | 1                                                                                                                                                                                                                                                                               | 0                        | JESD22<br><u>A-111 (SMD)</u><br>B-106 <u>(PTH)</u> | TEST before and after RSH. SMD <u>parts</u> shall be fully submerged during test <u>and preconditioned per MSL rating</u> .             |  |  |  |  |

| 21 | Solderability                                        | SD   | 2            | DG         | 10                                           | 1<br>Note B                                                                                                                                                                                                                                                                     | 0                        | J-STD-002<br><u>JESD22B102</u>                     | Magnification 50x, Reference solder conditions in Table 2B. Apply test method A for through-hole, or both test methods B and D for SMD. |  |  |  |  |

| 22 | Thermal<br>Resistance                                | TR   | 3            | DG         | 10 <u>each,</u><br>pre- &<br>post-<br>change | 1                                                                                                                                                                                                                                                                               | 0                        | JESD24-3, 24-<br>4, 24-6 as<br>appropriate         | Measure TR to assure specification compliance and provide process change comparison data.                                               |  |  |  |  |

| 23 | Wire Bond<br>Strength                                | WBS  | 3            | DGE        | 10 bonds<br>from min of<br>5 parts           | 1                                                                                                                                                                                                                                                                               | 0                        | MIL-STD-750<br>Method 2037                         | Pre- & Post-process change comparison to evaluate process change robustness.                                                            |  |  |  |  |

| 24 | Bond Shear                                           | BS   | 3            | DGE        | 10 bonds<br>from min of<br>5 <u>parts</u>    | 1                                                                                                                                                                                                                                                                               | 0                        | AEC-Q101-003                                       | See attached procedure for details on acceptance criteria and how to perform the test.                                                  |  |  |  |  |

| 25 | Die Shear                                            | DS   | 3            | DG         | 5                                            | 1                                                                                                                                                                                                                                                                               | 0                        | MIL-STD-750<br>Method 2017                         | Pre- & Post-process change comparison to evaluate process change robustness.                                                            |  |  |  |  |

|           | TABLE 2 - QUALIFICATION TEST DEFINITIONS (Continued) |            |              |           |                           |              |                          |                                    |                                                                                                                                                            |  |  |  |  |

|-----------|------------------------------------------------------|------------|--------------|-----------|---------------------------|--------------|--------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| #         | Stress                                               | Abrv       | Data<br>Type | Note      | Sample<br>Size<br>per Lot | # of<br>Lots | Accept<br>on #<br>Failed | Reference<br>(current<br>revision) | Additional Requirements                                                                                                                                    |  |  |  |  |

| 26        | Unclamped<br>Inductive<br>Switching                  | UIS        | 3            | D         | 5                         | 1            | 0                        | AEC-Q101-004<br>Section 2          | Pre- & Post-process change comparison to evaluate process change robustness (Power MOS and internally clamped IGBTs only).                                 |  |  |  |  |

| 27        | Dielectric Integrity                                 | DI         | 3            | DM        | 5                         | 1            | 0                        | AEC-Q101-004<br>Section 3          | Pre- & Post-process change comparison to evaluate process change robustness. All parts must exceed gate breakdown voltage minimum (Power MOS & IGBT only). |  |  |  |  |

| <u>28</u> | Short Circuit Reliability Characterization           | <u>SCR</u> | <u>3</u>     | <u>DP</u> | <u>10</u>                 | 3<br>Note B  | <u>0</u>                 | AEC-Q101-006                       | For smart power parts only.                                                                                                                                |  |  |  |  |

| <u>29</u> | <u>Lead Free</u>                                     | <u>LF</u>  | <u>3</u>     |           | =                         | =            | Ξ                        | AEC-Q005                           | For all related solderability, solder heat resistance and whisker requirements.  To be implemented on, or before, April 1, 2014.                           |  |  |  |  |

<sup>\*</sup> Note: All electrical testing before and after the qualification stresses (including pre-conditioning) are performed to the limits detailed in the individual user specification at room temperature only. For generic qualifications, the supplier's standard specification limits at room temperature may be used.

**Component Technical Committee**

#### **LEGEND FOR TABLE 2**

#### Notes:

- A For parametric verification data, sometimes circumstances may necessitate the acceptance of only one lot by the user. Should a subsequent user decide to use a previous user's qualification approval, it will be the subsequent user's responsibility to verify an acceptable number of lots were used.

- B Where generic (family) data is provided in lieu of component specific data, 3 lots are required.

- C Not applicable for LED's, phototransistors, and other optical parts.

- D Destructive test, <u>parts</u> are not to be reused for qualification or production.

- E Ensure that each size wire is represented in the sample size.

- For dissimilar metal bonding systems only (e.g., Au/Al).

- G Generic data allowed. See Section 2.3.

- H Required for hermetic packaged <u>parts</u> only. Items #16 through #19 are performed as a sequential test to evaluate mechanical integrity of packages containing internal cavities. Number in parentheses below notes indicates sequence.

- K Not applicable to voltage regulators (Zeners)

- L Required for leaded parts only.

- M Required for MOS & IGBT parts only.

- N Nondestructive test, parts can be used to populate other tests or they can be used for production.

- O Required for Voltage Regulators (Zeners) only.

- P Consideration should be made for whether this test is to be applied to a Smart Power <u>part</u> or substituted for a Q100 test. Elements for consideration include the amount of logic/sensing on the die, intended user application, switching speed, power dissipation, and pin count.

- S Required for surface mount <u>parts</u> only.

- T When testing diodes under Intermittent Op Life conditions the 100 degree junction temperature delta may not be achievable. Should this condition exist, a Power Temperature Cycling (Item 10alt) test shall be used in place of Intermittent Op Life (Item 10) to ensure the proper junction temperature changes occur. All other parts should use IOL.

- U For these tests only, it is acceptable to use unformed leaded packages (e.g., IPAK) to qualify new die going in the equivalent package (e.g., DPAK) provided the die size is within the range of sizes qualified for the equivalent package.

- V For bi-directional Transient Voltage Suppressor (TVS) devices, one-half the test duration in each direction shall be performed.

- W Not required for Transient Voltage Suppressor (TVS) <u>parts</u>. For TVS <u>parts</u>, PV data in <u>Section</u> 4.2 will be after 100% Peak Pulse Power (Pppm) has been performed to rated Ippm current.

- Y For switching parts (e.g., fast/ultrafast rectifiers, Schottkys) the rated junction temperature specified in the user/supplier specifications refers to a switch mode application condition. For those parts that can experience thermal runaway in HTRB using a DC reverse condition on a switch mode part, the maximum rated junction temperature at the rated DC Reverse Voltage may not be specified in the user/supplier specification and those test conditions should be stated in the qualification test plan/report. Example: for a 100V Schottky part; 100V would be applied with T<sub>A</sub> adjusted to maximum T<sub>J</sub> capability without driving part into thermal runaway, Voltage, T<sub>A</sub> and T<sub>J</sub> achieved would be reported as test conditions in the qualification test plan/report.

- Y Required for Thyristors only.

- Z Required for LEDs only.

- 1 Required for MOSFETs parts with internal bond wire sizes 5 mil diameter and less.

**Component Technical Committee**

Table 2A: <u>Timing Requirements for Intermittent Operational Life (Test #10) or Power Temperature</u>

<u>Cycling (Test #10alt)</u>

| Package Type | Number of Cycles Required $\Delta T_J \ge 100^{\circ}C$ | Number of Cycles Required $\Delta T_J \ge 125^{\circ}C$ | Time per cycle                                                 |

|--------------|---------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|

| All          | 60,000/(x+y)<br>15,000 cycles                           | 30,000/(x+y)<br>7,500 cycles                            | Fastest capable (minimum 2 min. on/off) x min. on + y min. off |

Example 1: A package capable of 2 minutes on/4 minutes off would require 10,000 cycles [60,000/(2+4)] at  $\Delta T_J \ge 100^{\circ}\text{C}$  or 5,000 cycles at  $\Delta T_J \ge 125^{\circ}\text{C}$ .

Example 2: A package capable of 1 minute on/1 minute off would require 15,000 cycles at  $\Delta T_J \ge 100^{\circ} C$  or 7,500 cycles at  $\Delta T_J \ge 125^{\circ} C$ .

X = the minimum amount of time it takes for the part to reach the required  $\Delta Tj$  from ambient temperature.

Y = the minimum amount of time it takes for the part to cool to ambient temperature from the required  $\Delta T_i$ .

The method of instrumentation, part mounting and heat sinking on the test board will influence x and y per package.

Table 2B: Solderability Requirements (Test #21) for SnPb Plated Terminations

| Tuno                           | Test   | Solder      | Steam Age | Exception for                          |

|--------------------------------|--------|-------------|-----------|----------------------------------------|

| Туре                           | Method | Temperature | Category  | Dry Heat                               |

| Leaded Through-Hole            | Α      | 235°C       | 3         |                                        |

| SMD Standard Process           | В      | 235°C       | 3         |                                        |

| SMD Low Temperature Solder     | В      | 215°C       |           | 4hrs @ 155°C<br>(in lieu of steam age) |

| SMD Dissolution of Metals test | D      | 260°C       | 3         |                                        |

<sup>\*</sup> Note: Refer to AEC - Q005 Pb-Free Test Requirements for solderability requirements of Pb-free terminated parts.

**Component Technical Committee**

#### **Table 3: Process Change Guidelines for the Selection of Tests**

Note: A letter or "•" indicates that performance of that stress test should be considered for the appropriate process change

| Note: A letter o                | r "●            | " inc                   |                     | es tn                | iat p             | ertori                  |                   |                             |                  | ess                  | test                    | snou                | ıla t             | ре <u>с</u>            | ons                   | ıdeı      | red              | tor t       | ne a                   | appı                     | opri               | ate p              | roce            | <u> 288</u>                                      | cnang                   | 2                                                | ı —                                        |       |

|---------------------------------|-----------------|-------------------------|---------------------|----------------------|-------------------|-------------------------|-------------------|-----------------------------|------------------|----------------------|-------------------------|---------------------|-------------------|------------------------|-----------------------|-----------|------------------|-------------|------------------------|--------------------------|--------------------|--------------------|-----------------|--------------------------------------------------|-------------------------|--------------------------------------------------|--------------------------------------------|-------|

| Table 2 Test #                  | 3               | 4                       | 5/<br><u>abc</u>    | 6                    | 7                 | <u>7ab</u>              | 8/<br><u>alt</u>  | 9/<br>alt <u>/a</u>         | 10/<br>alt       | 11                   | 12                      | 13                  | 14                | 15                     | 16                    | 17        | 18               | 19          | 20                     | 21                       | 22                 | 23                 | 24              | 25                                               | 26                      | 27                                               | <u>28</u>                                  |       |

| Test Name                       |                 |                         | / SSOP              |                      |                   | VBI                     |                   | 위                           |                  |                      | s                       |                     |                   | ø                      |                       |           |                  |             |                        | 005                      |                    |                    |                 |                                                  | 5                       |                                                  | 7                                          |       |

|                                 | External Visual | Parametric Verification | HTRB/ACBV/HTFB/SSOP | High Temp. Gate Bias | Temperature Cycle | TC Hot / TC Delam / WBI | UHAST / Autoclave | HAST / H³TRB <u>/ HTHHB</u> | 입                | ESD Characterization | Destruct. Phy. Analysis | Physical Dimensions | Terminal Strength | Resistance to Solvents | Constant Acceleration | u         | Mechanical Shock | icity       | Resist. to Solder Heat | Solderability / AEC-Q005 | Thermal Resistance | Wire Bond Strength | Wire Bond Shear | aar                                              | Unclamp. Induct. Switch | Dielectric Integrity                             | Short Circuit Reliability Characterization |       |

| Change                          | Externa         | Parame                  | HTRB /              | High Te              | Tempe             | TC Hot                  | UHAST             | HAST/                       | IOL <u>/ PTC</u> | ESD CI               | Destruc                 | Physica             | Termin            | Resista                | Consta                | Vibration | Mechai           | Hermeticity | Resist.                | Soldera                  | Therma             | Wire Bo            | Wire Bo         | Die Shear                                        | Unclan                  | Dielect                                          | Short C<br>Charac                          | NOTES |

| DESIGN                          |                 |                         |                     |                      |                   |                         |                   |                             |                  |                      |                         |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 |                                                  |                         |                                                  |                                            |       |

| Wafer Thickness                 |                 | •                       | •                   |                      | •                 | •                       |                   |                             | •                |                      | •                       |                     |                   |                        |                       |           |                  |             | Х                      |                          | •                  | •                  | •               |                                                  |                         |                                                  |                                            | F     |

| Wafer Diameter                  |                 | •                       | •                   | •                    |                   |                         |                   |                             |                  |                      |                         |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 | İ                                                |                         |                                                  |                                            |       |

| Die Size                        |                 | •                       | •                   |                      | •                 |                         |                   |                             | •                | Ε                    | •                       |                     |                   |                        |                       |           |                  |             | •                      |                          | •                  |                    |                 | •                                                | М                       |                                                  | •                                          | F     |

| Layout                          |                 | •                       | •                   | •                    | 3                 |                         |                   |                             | •                | Ε                    | 3                       |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 | İ                                                | М                       |                                                  | •                                          |       |

| Field Termination               |                 | •                       | •                   |                      | •                 |                         | •                 | •                           |                  | Е                    | •                       |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 |                                                  | М                       |                                                  |                                            |       |

| WAFER FAB                       |                 |                         |                     |                      |                   |                         |                   | •                           | •                |                      |                         |                     | •                 | •                      | •                     | •         | •                | •           |                        |                          |                    | •                  |                 |                                                  | •                       |                                                  |                                            | •     |

| Wafer Source                    |                 | •                       | •                   |                      |                   |                         |                   | •                           | •                |                      |                         |                     |                   |                        |                       |           |                  |             |                        |                          | •                  |                    |                 |                                                  | 9,M                     |                                                  |                                            | R     |

| Lithography                     |                 | •                       | 4                   | 4                    |                   |                         |                   | 6,7                         |                  |                      |                         |                     |                   |                        |                       |           |                  |             |                        |                          |                    | 1                  |                 |                                                  |                         |                                                  |                                            | Р     |

| Diffusion                       |                 | •                       | 5,6                 | 5                    |                   |                         | <u>6</u>          | 6                           |                  | •                    | 6                       |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 |                                                  | М                       |                                                  |                                            | PR    |

| Doping Profile/Schottky Barrier |                 | •                       | 5,0                 |                      |                   |                         |                   |                             |                  | •                    |                         |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 |                                                  | М                       |                                                  |                                            | R     |

| Ion Implantation                |                 | •                       | 5,6                 | •                    |                   |                         | <u>6</u>          | 6                           |                  | •                    | 6                       |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 |                                                  | М                       |                                                  |                                            | PR    |

| Polysilicon                     |                 | •                       | •                   | •                    | •                 |                         |                   |                             |                  | Е                    | •                       |                     |                   |                        |                       |           |                  |             |                        |                          |                    |                    |                 | 1                                                | М                       | •                                                | •                                          | Р     |

| Metallization (Top side)        |                 | •                       | 8                   |                      | •                 | •                       | •                 | •                           | •                | Ε                    | •                       |                     |                   |                        |                       |           |                  |             | •                      |                          |                    | •                  | •               |                                                  |                         | 1                                                | •                                          |       |