Automotive Electronics Council

Component Technical Committee

# **ATTACHMENT 5**

## AEC - Q101-005 Rev-A

# CHARGED DEVICE MODEL (CDM)

# **ELECTROSTATIC DISCHARGE (ESD) TEST**

## Automotive Electronics Council -----

Component Technical Committee

#### **Acknowledgment**

Any document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:

#### Charged Device Model Sub-Committee Members:

| Wolfgang Reinprecht                   | AMS                      |

|---------------------------------------|--------------------------|

| Alan Righter [Sub-Committee Co-Chair] | Analog Devices           |

| Mark Kelly                            | Aptiv                    |

| Reinhold Gaertner                     | Infineon Technologies    |

| Brett Carn                            | Intel Corporation        |

| <u>C.K. Barlingay</u>                 | <u>Microchip</u>         |

| Nick Martinez                         | <u>Microchip</u>         |

| Robert Ashton                         | <u>Minotaur Labs</u>     |

| <u>Greg O'Sullivan</u>                | <u>Micron</u>            |

| <u>Melissa Uribe</u>                  | <u>Micron</u>            |

| Bob Knoell                            | NXP Semiconductors       |

| Zhongning Liang                       | NXP Semiconductors       |

| Nick Lycoudes                         | NXP Semiconductors       |

| <u>Theo Smedes</u>                    | NXP Semiconductors       |

| Michael Stevens                       | NXP Semiconductors       |

| <u>Peter Turlo</u>                    | ON Semiconductor         |

| <u>Bassel Atala</u>                   | STMicroelectronics       |

| <u>Marty Johnson</u>                  | Texas Instruments        |

| Scott Ward [Sub-Committee Co-Chair]   | <u>Texas Instruments</u> |

| <u>James Williams</u>                 | <u>Texas Instruments</u> |

| Kun-Fu Chuang                         | Winbond Corporation      |

| <u>Dean Tsaggaris</u>                 | <u>Xilinx</u>            |

|                                       |                          |

**Component Technical Committee**

### NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.

AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.

AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in conformance with this document shall be made unless all requirements stated in the document are met.

Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link http://www.aecouncil.com.

Published by the Automotive Electronics Council.

This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

Printed in the U.S.A. All rights reserved

<u>Copyright © 2019 by the Automotive Electronics Council. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Technical Committee.</u>

Component Technical Committee

# **Change Notification**

### The following summary details the changes incorporated into AEC-Q101-005 Rev-A:

- <u>Added Cover Page, Acknowledgement Page, Notice Page, and Change Notification</u>

<u>Page.</u>

- <u>Section 1.2, Reference Documents: Added ANSI/ESDA/JEDEC JS-002 standard</u> <u>document reference and deleted ESDA S5.3.1 and JEDEC JESD22-C101 standard</u> <u>document references.</u>

- <u>NEW Section 2, Additional Requirements (addendum to JS-002): Added new section</u> of specific AEC-Q101-005 requirements beyond those stated in JS-002, including:

- Section 2.1, Tester and Device Preparation

- o Section 2.2, Measurements

- o Section 2.3, Sample Size

- o Section 2.4, Discharge Requirements

- o Section 2.5, Detailed Procedure

- o Section 2.6, Small Package Considerations

- o Section 2.7, Wafer or Bare Die Considerations

- o Section 2.8, Failure Criteria

- o Section 2.9, Acceptance Criteria

- Section 2.10, Test Reporting

- <u>NEW Table 2, Discrete Semiconductor CDM ESD Classification Levels: Modified</u> <u>content of Table 2 to align Classification Levels and Maximum Withstand Test</u> <u>Condition Levels with JS-002.</u>

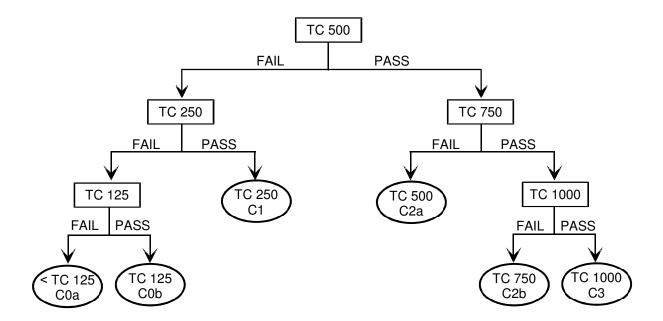

- <u>NEW Figure 1, Recommended Discrete Semiconductor CDM ESD Test Flow Diagram:</u> <u>Modified content of Figure 1 to align Classification Levels and Maximum Withstand Test</u> <u>Condition Levels with Table 2 and JS-002.</u>

**Component Technical Committee**

### METHOD - 005

### DISCRETE SEMICONDUCTOR CHARGED DEVICE MODEL (CDM) ELECTROSTATIC DISCHARGE (ESD) TEST

All CDM ESD testing performed on Discrete Semiconductor devices to be AEC Q101 qualified shall be per the latest version of the ANSI/ESDA/JEDEC JS-002 specification with the following clarifications and requirements. Text enhancements and differences made since the last revision of this document are shown as underlined areas.

1. SCOPE

#### 1.1 Description

The purpose of this specification is to establish a reliable and repeatable procedure for determining the CDM ESD sensitivity for <u>discrete semiconductor devices</u>.

#### 1.2 Reference Documents:

ANSI/ESDA/JEDEC JS-002, Charged Device Model (CDM), Device Level

#### 2. Additional Requirements (addendum to JS-002)

#### 2.1 <u>Tester and Device Preparation</u>

- 2.1.1 Devices used for CDM stressing shall not have been used for any prior stress tests.

- 2.1.2 ESD damage prevention procedures shall be used before, during, and after CDM and post parametric testing.

NOTE: See the latest revision of ANSI/ESD S20.20, JESD625, IEC 61340-5-1 or company-specific handling procedures for guidance.

**2.1.3** Devices shall be clean before testing. If needed, cleaning should be completed in compliance with company-approved procedures.

NOTE: Isopropanol (isopropyl alcohol) is typically used for cleaning.

**2.1.4** The CDM tester probe and field plate / dielectric shall be clean and dry before testing. Cleaning may be performed periodically or based on waveform acceptance using isopropanol (isopropyl alcohol).

NOTE: Surfaces should be allowed to dry before testing.

2.1.5 Determination and setting of CDM field plate voltage factor and voltage offsets may only be done during full qualification of the CDM test system. Voltage factors and voltage offsets may not be adjusted based on routine waveform verification or based on product test waveforms or results.

NOTE: Section 6.5.2 of JS-002 describes conditions requiring CDM test system qualification or - re-qualification.

**Component Technical Committee**

2.1.6 The same voltage factor adjustments and voltage offsets from qualification shall be used for product at all test conditions and polarities. The qualification procedure described in JS-002 Annex G.1 shall be used for both positive and negative stress determination of offsets to provide separate uniform positive stress offsets and uniform negative stress offsets.

#### 2.2 Measurements

Prior to ESD testing, complete parametric testing (initial electrical verification) shall be performed on all sample groups and all <u>devices</u> in each sample group per applicable user device specification at room temperature followed by hot temperature, unless specified otherwise in the user device specification. A data log of each <u>device</u> shall be made listing all parameter measurements as defined in Table <u>1</u>. The data log will be compared to the parameters measured during final electrical verification testing to determine the failure criteria of <u>Section 2.8</u>.

#### 2.3 Sample Size

Each sample group shall be composed of ten (10) <u>devices</u> per stress <u>test condition</u>. Each sample group shall have all device pins and/or terminals stressed at one (1) <u>test condition</u> level, following the <u>recommended</u> test flow diagram of Figure <u>1</u>. Each stress <u>test condition</u> requires a new sample group of ten (10) <u>devices</u>.

#### 2.4 Discharge Requirements

The use of three (3) discharges at each stress level is required. Three (3) positive followed by three (3) negative discharges is also allowed, as well as three alternating sets of positive and negative discharges. Please refer to Annex F of JS-002 for detailed procedure of the single and dual discharge procedures.

#### 2.5 Detailed Procedure

The ESD testing procedure shall be per <u>one of the three options below:</u>

#### 2.5.1 CDM ESD Test Procedure - Option 1

Separate test sample groups shall be submitted for every classification test condition per Section 2.9 and Figure 1 followed by functional testing.

#### 2.5.2 CDM ESD Test Procedure - Option 2

Test samples shall be submitted for the lowest starting test condition per Section 2.9 and Figure 1 followed by functional test. If all samples pass, the same samples, or fresh samples, are then stressed at the next higher classification test condition and functionally tested. This procedure shall be followed until the failing test condition is reached or the samples pass TC 1000.

#### 2.5.3 CDM ESD Test Procedure - Option 3

The ESD testing procedure shall be per the recommended test flow of Figure 1 and as follows:

- a. Place clean DUT "dead-bug" with <u>device</u> body in direct contact with the <u>dielectric on top</u> <u>of the field plate</u>.

- b. Follow the recommended test flow diagram of Figure <u>1</u>. <u>Set the test condition stress level</u> <u>to positive TC 500.</u>

- c. <u>Elevate the potential of the DUT by applying the TC 500 stress level to the field plate.</u>

Component Technical Committee

- d. Select a PUT and ground (discharge) the DUT, using either discharge method as described in Annex F of JS-002.

- e. <u>If using the single discharge procedure, set the test condition stress level</u> to negative <u>TC 500, select the same PUT as in step (d) and ground (discharge) the DUT. If using the dual discharge procedure, this step has already been completed.</u>

- f. Repeat steps (c) through (e) using the <u>next</u> PUT. <u>The use of a new sample group for</u> <u>each stress polarity is also acceptable.</u>

- g. Repeat steps (b) through (f) until every PUT (all <u>device</u> pins, <u>including power and ground</u> <u>pins</u>) is discharged at the specified <u>test condition level and polarity</u>.

- h. Test the next <u>device</u> in the sample group and repeat steps (a) through (g) until all <u>devices</u> in the sample group have been tested at the specified <u>test condition</u> level <u>and polarity</u>.

- i. Submit the <u>devices</u> for complete parametric testing (final electrical verification) per the user device specification at room temperature followed by hot temperature, unless specified otherwise in the user device specification, and determine whether the <u>devices</u> meet the <u>acceptance</u> criteria specified in <u>Section 2.9</u>. It is permitted to perform the parametric testing (final electrical verification) per user device specification after all sample groups have been <u>stressed</u>.

- j. Using the next sample group, select the next <u>test condition stress</u> level as specified in Figure <u>1</u> and repeat steps (a) through (i).

- k. Repeat steps (a) through (j) until failure occurs or the <u>device</u> fails to meet the <u>TC 125</u> stress <u>test condition</u>.

#### 2.6 Small Package Considerations

CDM testing of discrete semiconductors in small packages is very challenging. The vacuum used to hold the package in place during testing is not effective when the package is under a few square millimeters. The capacitance between the device under test and the field plate is also very small, which results in very fast CDM current pulses. These pulses have non-negligible peak currents, but have very fast rise times and very narrow pulse widths, making the pulses impossible to measure with standard 1 GHz measurement systems. Additionally, the total charge within the pulses is so small that CDM failures of discrete semiconductors in very small packages have seldom been seen. For these reasons, the testing of discrete semiconductors in very small packages is often not performed (as agreed between supplier and customer) due to the difficulty of testing and the very low chance of failure. Any device or package that could not be completely CDM stressed due to package size shall be recorded.

#### 2.7 Wafer or Bare Die Considerations

The test methods described in this standard may also be used to evaluate devices that are shipped as wafers or bare dice. Standardized CDM stressing of wafers or bare dice is not defined due to equipment limitations. Products shipped as bare dice may be placed in a package for purposes of performing CDM stressing, as determined by package test limitations and agreement between supplier and customer. The package used for this stressing shall be recorded.

**Component Technical Committee**

#### 2.8 Failure Criteria

A <u>device</u> will be defined as a failure if, after exposure to ESD pulses, the <u>device</u> fails any of the following criteria:

- <u>a</u>. The <u>device</u> exceeds the allowable shift values for the specific key parameters listed in Table <u>1</u>. Other <u>device</u> parameters and allowable shift values may be specified in the user device specification. During initial parametric testing, a data log shall be made for each <u>device</u> listing the applicable parameter measurement values. This data log will be compared to the parameters measured during final parametric testing to determine the shift value. Devices exceeding the allowable shift value will be defined as a failure.

- <u>b</u>. The <u>device</u> no longer meets the user device specification requirements. Complete parametric testing (initial and final electrical verification) shall be performed per applicable user device specification at room temperature followed by hot temperature, unless specified otherwise in the user device specification.

| <u>Device</u> Type | Parameters           | Maximum Allowable Shift Values          |

|--------------------|----------------------|-----------------------------------------|

| Bipolar            | ICES, ICBO, and IEBO | Ten times (10X) the initial measurement |

| FET                | IDSS and IGSS        | Ten times (10X) the initial measurement |

| IGBT               | ICES and IGES        | Ten times (10X) the initial measurement |

| Diode              | IR                   | Ten times (10X) the initial measurement |

#### Table 1: Key Parameters and Allowable Shift Values

#### 2.9 Acceptance Criteria

A <u>device</u> passes a <u>stress test condition</u> level if all <u>devices</u> stressed at that <u>test condition</u> level and below pass. All the samples must meet the measurement requirements specified in <u>Section 2.2</u> and the failure criteria requirements specified in <u>Section 2.8</u>. Using the classification levels specified in Table <u>2</u>, the supplier shall classify the <u>devices</u> according to the maximum withstand <u>test condition</u> level. Due to the complex nature of the CDM event, a change in manufacturing process, design, materials, or <u>device</u> package may require reclassification according to this test method.

Component Technical Committee

| Classification Level | Maximum Withstand Test Condition  |

|----------------------|-----------------------------------|

| C0 <u>a</u>          | < <u>TC</u> 125                   |

| C <u>0b</u>          | <u>TC</u> 125 to < <u>TC</u> 250  |

| C <u>1</u>           | <u>TC</u> 250 to < <u>TC</u> 500  |

| C <u>2a</u>          | <u>TC 500 to &lt; TC 750</u>      |

| C <u>2b</u>          | <u>TC</u> 750 to < <u>TC</u> 1000 |

| C <u>3</u>           | <u>TC</u> 1000 <sup>[1]</sup>     |

### Table 2: Discrete Semiconductor CDM ESD Classification Levels

[1] For test conditions above TC 1000, depending on geometry of the device package, corona effects may limit the actual pre-discharge voltage and discharge current.

Figure 1: <u>Recommended</u> Discrete <u>Semiconductor</u> CDM ESD Test Flow Diagram

**Component Technical Committee**

### 2.10 Test Reporting

Upon completion of the required testing defined herein, a report of the testing performed and detailed results, as defined below, including any deviations, shall be submitted to the user upon request.

- a. Sample Details

- Package configuration (e.g., lead pitch, pin count, lead form, etc.)

- Sample sizes

- b. Test Details

- Discharging method (e.g., single or dual)

- <u>Stress test condition (TC) levels</u>

- <u>Test/Pin partitioning (if applicable)</u>

- Package orientation during testing

- Exceptions to any tests performed

- Special considerations for small packages

- Mounting package on a surrogate

- o Wafer/bare die

- c. Test Results

- Summary of results

Component Technical Committee

# **Revision History**

Rev #

Date of change

Brief summary listing affected sections

July 18, 2005

Initial Release.

A

Jan. 29, 2019

Complete revision. Added reference to ANSI/ESDA/JEDEC JS-002 as accepted Charged Device Model Standard document. Added new Section 2, Additional Requirements (addendum to JS-002), listing specific AEC-Q101-005 requirements beyond those stated in JS-002.