AEC - Q004 - Rev-February 26, 2020

## AUTOMOTIVE ZERO DEFECTS FRAMEWORK

#### Automotive Electronics Council Component Technical Committee

## Automotive Electronics Council — Component Technical Committee

Page intentionally left blank

#

### TABLE OF CONTENTS

| 1. SC | COPE                                                          | 1  |

|-------|---------------------------------------------------------------|----|

| 1.1.  | Purpose                                                       | 1  |

| 1.2.  | Reference Documents                                           | 2  |

| 1.3.  | Definitions and Acronyms                                      | 3  |

| 1.4.  | Zero defects and Quality Management                           | 6  |

| 2. AP | PLICATION OF THE ZERO DEFECTS FRAMEWORK                       | 6  |

| 2.1.  | General                                                       | 6  |

| 2.2.  | Safe Launch                                                   | 7  |

| 2.3.  | Cost Benefit Analysis                                         | 7  |

| 3. PR | ODUCT DESIGN                                                  | 10 |

| 3.1.  | Design Failure Mode and Effect Analysis (DFMEA)               | 10 |

| 3.2.  | Redundancy                                                    | 11 |

| 3.3.  | Built-in Self-Test                                            | 12 |

| 3.4.  | Design for Test                                               | 14 |

| 3.5.  | Design for Analysis                                           | 16 |

| 3.6.  | Design for Manufacturability                                  | 17 |

| 3.7.  | Design for Reliability                                        | 18 |

| 3.8.  | Simulation and Modeling                                       | 20 |

| 3.9.  | Characterization                                              | 22 |

| 4. MA | ANUFACTURING                                                  |    |

| 4.1.  | Process Failure Mode and Effect Analysis (PFMEA)              |    |

| 4.2.  | Statistical Analysis of Variance                              |    |

| 4.3.  | Control Plan                                                  |    |

| 4.4.  | Statistical Process Control                                   |    |

| 4.5.  | Lot Acceptance Gates                                          |    |

| 4.6.  | Audits (Management System, Manufacturing Process and Product) | 29 |

| 5. TE | ST                                                            | 30 |

| 5.1.  | Part Average Testing                                          | 30 |

| 5.2.  | Statistical Bin Yield Analysis                                | 31 |

| 5.3.  | Data Collection, Storage and Retrieval                        | 32 |

| 5.4.  | Screens                                                       | 33 |

| 6. AP | PLICATION AND CAPABILITY                                      | 34 |

| 6.1.  | Industry Standards                                            | 34 |

| 6.2.  | Environmental Stress Testing                                  | 35 |

| 6.3.  | Stress-Strength Analysis                                      | 36 |

| 6.4.  | Systems Engineering                                           | 37 |

| 6.5.  | Product Derating                                              |    |

## Automotive Electronics Council — Component Technical Committee

## TABLE OF CONTENTS (continued)

| 7. COI | NTINUOUS IMPROVEMENT METHODS     | 40 |

|--------|----------------------------------|----|

| 7.1.   | Wafer Level Process Monitoring   | 40 |

| 7.2.   | Process and Product Improvements | 41 |

| 7.3.   | Product Reliability Monitoring   | 42 |

| 7.4.   | Defect Monitoring                | 43 |

| 8. PR0 | OBLEM SOLVING                    | 45 |

| 8.1.   | Problem Solving Techniques       | 45 |

| 8.2.   | Failure Analysis Process         | 46 |

| 9. DO  | CUMENTATION                      | 48 |

**Component Technical Committee**

#### Acknowledgment

Any document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:

#### AEC-Q004 Zero Defects Framework Sub-Committee Members:

Prasad Dhond **Bruce Hecht** James Johnston Ashok Alagappan James McLeish David Locker Jeff Jarvis Carsten Ohlhoff Gary Fisher Michael Brucker Ludger Kappius [Q004 Sponsor] Ulrich Abelein Ken Berry Sultan Lilani lfe Hsu Banjie Bautista Robert Kinyanjui David Price Jay Rathert Colman Byrne Tom Lawler John Grogan Tom VanDamme Wilhelm Binder Melissa Uribe Carmen Cotofana Rene Rongen [Q004 Team Leader] Joop Verwijst Peter Turlo Daniel Vanderstraeten Lakshmi Kari Holger Neumann Jason Engel **Bassel Atala** James Williams Arthur Chiang Kun-Fu Chuang

AMKOR Analog Devices Analog Devices ANSYS / DfR Solutions ANSYS / DfR Solutions CCDC-AvMC CCDC-AvMC **Continental Automotive** Gentex GlobalFoundries Hella Infineon Technologies Infineon Technologies Integra Technologies Intel ISSI John Deere Electronic Solutions, Inc. KLA KLA Kostal Lattice Semiconductor Macronix International Magna Microchip Micron Nexperia NXP Semiconductors NXP Semiconductors **ON Semiconductor ON Semiconductor** Qualcomm Sensata Technologies Silicon Labs **STMicroelectronics Texas Instruments** Vishay Winbond

**Component Technical Committee**

#### NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.

AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.

AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in Conformance with this document shall be made unless all requirements stated in the document are met.

Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link http://www.aecouncil.com.

Published by the Automotive Electronics Council.

This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

Printed in the U.S.A. All rights reserved

Copyright © 2020 by the Automotive Electronics Council. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.

Component Technical Committee

## ZERO DEFECTS FRAMEWORK

#### 1. SCOPE

This document provides a framework to be used in the definition of a strategy towards Zero Defects (ZD) of any semiconductor product in the scope of the AEC-Q100, -Q101, -Q102, -Q103, and -Q104 standards and, where applicable, passive components in AEC-Q200. The list of processes, methods and tools in this framework are based on industry best practices and Suppliers may use other internally developed and proprietary methods to reduce defects.

#### 1.1. Purpose

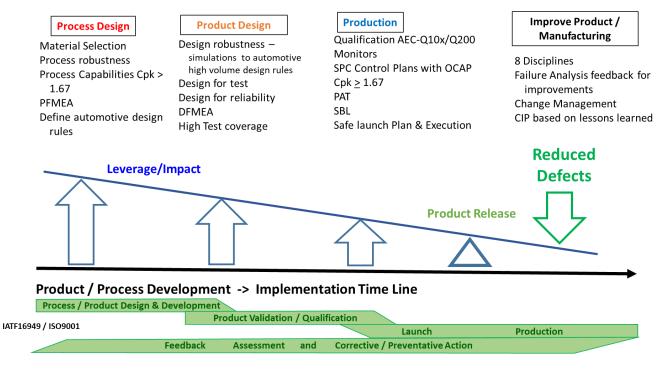

The purpose of this ZD framework is to enable the semiconductor Suppliers to select from a list of best practices, commonly used in the industry, that are appropriate to their products to drive to zero defects through the phases of process design, product design, production, and product/manufacturing Improvement, as depicted in Figure 1.

Figure 1: Zero Defects Framework – Progression towards ZD

##

#### 1.2. **Reference Documents**

### Table 1: List of references

| Document ID                                                                               | Title                                                                                                                                            | Section  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| <b>Automotive Electron</b>                                                                | hics Council (AEC) Weblink: http://www.aecouncil.c                                                                                               | com/     |  |  |  |  |  |

| AEC-Q100                                                                                  | Failure Mechanism Based Stress Test Qualification for<br>Integrated Circuits                                                                     | 6.1, 6.2 |  |  |  |  |  |

| AEC-Q101                                                                                  | Failure Mechanism Based Stress Test Qualification for<br>Discrete Semiconductors                                                                 | 6.1, 6.2 |  |  |  |  |  |

| AEC-Q102                                                                                  | Failure Mechanism Based Stress Test Qualification for<br>Discrete Optoelectronic Semiconductors in Automotive<br>Applications6.1, 6.2            |          |  |  |  |  |  |

| AEC-Q103                                                                                  | Failure Mechanism Based Stress Test Qualification for<br>Sensors in Automotive Applications                                                      | 6.1, 6.2 |  |  |  |  |  |

| AEC-Q104                                                                                  | Failure Mechanism Based Stress Test Qualification for<br>Multichip Modules (MCM) In Automotive Applications                                      | 6.1, 6.2 |  |  |  |  |  |

| AEC-Q200                                                                                  | Stress Test Qualification for Passive Component                                                                                                  | 6.1, 6.2 |  |  |  |  |  |

| AEC-Q100-007                                                                              | Fault Simulation and Fault Grading                                                                                                               | 3.4, 3.8 |  |  |  |  |  |

| AEC-Q100-009                                                                              | Electrical Distribution Assessment                                                                                                               | 3.9      |  |  |  |  |  |

| AEC-Q001                                                                                  | Guidelines for Part Average Testing                                                                                                              | 5.1      |  |  |  |  |  |

| AEC-Q002                                                                                  | Guidelines for Statistical Yield Analysis                                                                                                        | 5.2      |  |  |  |  |  |

| AEC-Q003                                                                                  | Guidelines for Characterizing the Electrical Performance of<br>Integrated Circuit Products                                                       | 3.9      |  |  |  |  |  |

| AEC-Q006                                                                                  | Qualification Requirements for Components using Copper (Cu) Wire Interconnects                                                                   | 6.1, 6.2 |  |  |  |  |  |

| Automotive Industry                                                                       | / Action Group (AIAG) Weblink: https://www.aiag.org/                                                                                             |          |  |  |  |  |  |

| AIAG APQP                                                                                 | Advanced Product Quality Planning & Control Plan                                                                                                 | 4.3, 6.4 |  |  |  |  |  |

| AIAG SPC                                                                                  | Statistical Process Control                                                                                                                      | 4.4      |  |  |  |  |  |

| AIAG FMEA                                                                                 | AIAG & VDA FMEA Handbook                                                                                                                         | 3.1, 4.1 |  |  |  |  |  |

| AIAG PPAP                                                                                 | Production Part Approval Process                                                                                                                 | 4.4      |  |  |  |  |  |

| <b>Electronic Industries</b>                                                              |                                                                                                                                                  |          |  |  |  |  |  |

| EIA632                                                                                    | Processes for Engineering a System                                                                                                               | 6.4      |  |  |  |  |  |

|                                                                                           | otive Task Force (IATF) Weblink: https://www.iatfglobalc                                                                                         |          |  |  |  |  |  |

| IATF16949                                                                                 | International Automotive Task Force                                                                                                              | 4.6      |  |  |  |  |  |

| International Organi<br>(ISO)                                                             | zation for Standardization Weblink: https://www.iso.org/ho                                                                                       | me.html  |  |  |  |  |  |

| ISO26262                                                                                  | Road Vehicles – Functional Safety                                                                                                                | 3.2, 6.4 |  |  |  |  |  |

| ISO/IEC/IEEE15288                                                                         | System and Software Engineering – System Lifecycle<br>Processes                                                                                  | 6.4      |  |  |  |  |  |

| Solid State Technole                                                                      | ogy Association (JEDEC) Weblink: https://www.jedec.org/                                                                                          | ,        |  |  |  |  |  |

| JEP122                                                                                    | Failure Mechanisms and Models for Silicon Semiconductor<br>Devices                                                                               | 3.8      |  |  |  |  |  |

| JEP131                                                                                    | Process Failure Modes & Effects Analysis                                                                                                         | 3.1, 4.1 |  |  |  |  |  |

| JEP148                                                                                    | Reliability Qualification of Semiconductor Devices Based       3.7, 3.8         Upon Physics of Failure Risks and Applications       Assessments |          |  |  |  |  |  |

| JEP150                                                                                    | Stress Test Drive Qualification of and Failure Mechanisms       6.2         Associated with Assembled Solid-State Surface Mount       Components |          |  |  |  |  |  |

| JESD16                                                                                    | Assessment of Average Outgoing Quality Levels in Parts 4.5, 5.4<br>Per Million (PPM)                                                             |          |  |  |  |  |  |

| JESD22                                                                                    | Test Methods 6.1,                                                                                                                                |          |  |  |  |  |  |

| JESD46 Customer Notification of Product/Process Changes by 7.2<br>Semiconductor Suppliers |                                                                                                                                                  |          |  |  |  |  |  |

**Component Technical Committee**

| Document ID                                                                | Title                                                                                                                                                                    | Section               |  |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| Solid State Technology Association (JEDEC) Weblink: https://www.jedec.org/ |                                                                                                                                                                          |                       |  |  |  |  |  |

| JESD50                                                                     | Special Requirements for Maverick Product Elimination                                                                                                                    | 4.5, 5.1, 5.2,<br>5.4 |  |  |  |  |  |

| JESD74                                                                     | Early Life Failure Rate Calculation Procedure for Electronic 4.5, 5.4<br>Components                                                                                      |                       |  |  |  |  |  |

| JESD88                                                                     | JEDEC Dictionary of Terms for Solid-State Technology                                                                                                                     |                       |  |  |  |  |  |

| JESD94                                                                     | Application Specific Qualification Using Knowledge Based<br>Test Methodology                                                                                             | 6.2                   |  |  |  |  |  |

| JESD557                                                                    | Statistical Process Control Systems                                                                                                                                      | 4.5                   |  |  |  |  |  |

| JESD659                                                                    | Failure Mechanism Driven Reliability Monitoring                                                                                                                          | 7.3, 7.4              |  |  |  |  |  |

| JESD671                                                                    | Component Quality Problem Analysis and Corrective Action Requirements                                                                                                    | 8.1, 8.2              |  |  |  |  |  |

| Military Standards                                                         | Weblink: -                                                                                                                                                               |                       |  |  |  |  |  |

| MIL-PRF-19500                                                              | Performance Specification – Semiconductor Devices –<br>General Specification                                                                                             | 5.4                   |  |  |  |  |  |

| MIL-STD-883                                                                | Test Method Standard – Microcircuits                                                                                                                                     | 5.4                   |  |  |  |  |  |

| Society of Automoti                                                        | ve Engineers (SAE) Weblink: https://www.sae.org/                                                                                                                         |                       |  |  |  |  |  |

| SAE-ARP6338                                                                | Process for Assessment and Mitigation of Early Wear out of Life-Limited Microcircuits                                                                                    | 3.7                   |  |  |  |  |  |

| SAE-J1211                                                                  | Robustness Validation for Electrical/Electronic Modules – section 8 – Modeling Analysis and Simulation                                                                   | 3.7, 6.2              |  |  |  |  |  |

| SAE-J1879                                                                  | Handbook for Robustness Validation of Semiconductor<br>Devices in Automotive Applications                                                                                | 6.1, 6.2              |  |  |  |  |  |

| Document ID                                                                | Title                                                                                                                                                                    | Section               |  |  |  |  |  |

| SAE-J3083                                                                  | Reliability Prediction for Automotive Electronics Based on<br>Field Return Data                                                                                          | 3.8                   |  |  |  |  |  |

| Others                                                                     | Weblink: -                                                                                                                                                               |                       |  |  |  |  |  |

|                                                                            | Automotive SPICE – VDA QMC Automotive SPICE Process<br>Assessment Model                                                                                                  | 6.4                   |  |  |  |  |  |

|                                                                            | Design Structure Matrix Methods and Applications, S.D.<br>Eppinger and T.R. Browning (Feb 2016)                                                                          | 6.4                   |  |  |  |  |  |

|                                                                            | Engineering a Safer World: Systems Thinking Applied to Safety, N. Leveson (Jul 2012)                                                                                     | 6.4                   |  |  |  |  |  |

|                                                                            | 6.4                                                                                                                                                                      |                       |  |  |  |  |  |

|                                                                            | INCOSE Systems Engineering Handbook (2015)<br>MITRE Systems Engineering Guide (SEG)                                                                                      |                       |  |  |  |  |  |

|                                                                            | NIST/SEMATECH e-Handbook of Statistical Methods                                                                                                                          | 4.2                   |  |  |  |  |  |

|                                                                            | <i>Review on Redundancy in Electronics</i> , Mr. Gurudatt<br>Kulkarni and Prof. Mrs. Lalita Wani. International Journal of<br>Engineering and Computer Science, Nov 2013 | 3.2                   |  |  |  |  |  |

### Table 1: List of references (continued)

#### 1.3. Definitions and Acronyms

#### 1.3.1 Product / Component / Part / Unit / Device / Design / Chip / IC

Interchangeable descriptors frequently used in an informal manner of speaking depicting a physical entity that a semiconductor Supplier conceives and delivers to the general market or to specific Users. It is a solid state based electronic entity that is designed by the Supplier to serve a special purpose, or to perform a unique function is subsequently integrated into a larger electronic system conceived by the User. In the context of this document, the use of the word "*product*" will be standardized as much as possible to aid readability. Where applicable, on an exception basis, the use of other industry accepted synonyms better suited to the specific context may also be used. Commonly found synonyms in titles of other industry standards and methods, or historical references, are retained.

**Component Technical Committee**

#### 1.3.2 Safe Launch

Safe Launch is a practice defined for use when a product is introduced into production whether initial ramp by Manufacturer/Supplier or into a new project by User. The Safe Launch plan implements selected temporary controls to establish a baseline to achieve acceptable product quality. These temporary controls are typically more stringent during Safe Launch execution. Data from the Safe Launch execution is collected, monitored, and analyzed, and the Safe Launch plan may be adjusted accordingly.

#### 1.3.3 Data Mining

Automating the process of searching for patterns in a data set (e.g., cluster analysis and data classification).

#### 1.3.4 Degradation or Fatigue Defect

Typically a common cause or intrinsic failure that follows a trend.

#### 1.3.5 Extrinsic defect

Physical structural irregularity (e.g., nodule or particle or void).

#### 1.3.6 Spike

Exclusively used in combination with failure mode descriptions (e.g., electrical signal timing behavior and not for structural irregularities).

#### 1.3.7 NTF – No Trouble Found

Both the Supplier and User could not verify a reported failure; a returned component is deemed good or functional according to specifications.

#### 1.3.8 TNI – Trouble Not Identified

Failure mode still present but the failure mechanism and/or cause could not be isolated; failure mode changed or recovered during analysis so failure mechanism and/or cause of initial failure could no longer be identified.

#

### Table 2: List of Acronyms

| Acronym          | Description                                          | Acronym  | Description                                    |

|------------------|------------------------------------------------------|----------|------------------------------------------------|

| 8D               | Eight Disciplines of Problem Solving                 | JEP      | JEDEC Publication                              |

| A3/SPS           | Structured Problem-Solving Tool                      | JESD     | JEDEC Standard Document                        |

| AC               | Alternating Current                                  | Leff     | Effective Length                               |

| AEC              | Automotive Electronics Council                       | MIL-PRF  | Military Performance Specification             |

| AIAG             | Automotive Industry Action Group                     | MIL-STD  | Military Standard                              |

| ANOVA            | ANalysis Of Variance                                 | MITRE    | Massachusetts Institute of Technology          |

|                  |                                                      |          | Research & Engineering                         |

| AP               | Action Priority                                      | MSA      | Measurement Systems Analysis                   |

| APQP             | Advanced Product Quality Planning                    | NA       | Not Applicable                                 |

| ATE              | Automated Test Equipment                             | NIST     | National Institute of Standards and Technology |

| BIST             | Built-In Self-Test                                   | NTF      | No Trouble Found                               |

| BPT              | Bond Pull Test                                       | NVM      | Non-Volatile Memory                            |

| BST              | Bond Shear Test                                      | OCAP     | Out of Control Action Plan                     |

| BTI              | Biased Temperature Instability                       | PAT      | Part Average testing                           |

| CAE              | Computer Aided Engineering                           | PCN      | Product Change Notification                    |

| Ср               | Process Capability                                   | PFMEA    | Process Failure Mode and Effect Analysis       |

| Cpk              | Process Capability Index                             | PoF      | Physics of Fail                                |

| DC               | Direct Current                                       | Pp       | Process Performance                            |

| D <sub>cap</sub> | Drain Capacitance                                    | PPAP     | Production Part Approval Process               |

| DfA              | Design For Analysis                                  | Ppk      | Process Performance Index                      |

| DfM              | Design For Manufacturability                         | PPM      | Part Per Million                               |

| DFMEA            | Design Failure Mode and Effect Analysis              | QBD      | Charge to Breakdown                            |

| DfR              | Design For Reliability                               | QMC      | Quality Management Center                      |

| DfT              | Design For Testing                                   | ROM      | Read Only Memory                               |

| DfX              | Design For eXcellence                                | Rs       | Series Resistance                              |

| DOE              | Design Of Experiment                                 | SAE      | Society of Automotive Engineers                |

| DPM              | Defects Per Million                                  | SEG      | Systems Engineering Guide                      |

| EIA              | Electronic Industries Alliance                       | SEMATECH | Consortium for Semiconductor Manufacturing     |

|                  |                                                      |          | Technology                                     |

| EM               | ElectroMigration                                     | SIMS     | Secondary Ion Mass Spectroscopy                |

| EOL              | End Of Life                                          | SPC      | Statistical Process Control                    |

| FA               | Failure Analysis                                     | SPICE    | Software Process Improvement and Capability    |

|                  |                                                      |          | Evaluation                                     |

| FMEA             | Failure Mode and Effect Analysis                     | SRAM     | Static Random-Access Memory                    |

| GD&T             | Geometric Dimensioning and Tolerancing               | StDev    | Standard Deviation                             |

| HALT             | Highly Accelerated Life Testing                      | TDDB     | Time Dependent Dielectric Breakdown            |

| HASS             | Highly Accelerated Stress Screen                     | TNI      | Trouble Not Identified                         |

| HCI              | Hot Carrier Injection                                | UIS      | Unclamped Inductive Stress                     |

| HTOL             | High Temperature Operating Life                      | VDA      | Verband der Automobilindustrie - German        |

|                  |                                                      |          | Association of the Automotive Industry         |

| HVST             | High Voltage Stress Test                             | VLVT     | Very Low Voltage Test                          |

| IATF             | International Automotive Task Force                  | Vmax     | Maximum Voltage                                |

| IC               | Integrated Circuit                                   | Vmin     | Minimum Voltage                                |

| IDDQ             | Quiescent Supply Current                             | Vstress  | Stress Voltage                                 |

| IEC              | International Electrotechnical Commission            | Vt       | Threshold Voltage                              |

| IEEE             | Institute of Electrical and Electronics<br>Engineers | Vtn      | Threshold Voltage NMOST                        |

| INCOSE           | International Council on Systems Engineering         | Vtp      | Threshold Voltage PMOST                        |

| IP               | Intellectual Property                                | Vtyp     | Typical Voltage                                |

| ISO              | International Organization for Standardization       | WLR      | Wafer Level Reliability                        |

| JEDEC            | Solid State Technology Association (Formerly         | ZD       | Zero Defects                                   |

|                  | Joint Electron Device Engineering Council)           |          |                                                |

**Component Technical Committee**

#### 1.4. Zero defects and Quality Management

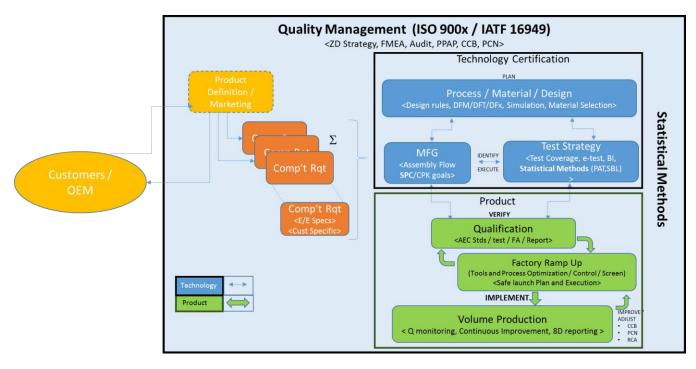

An alternative view on a Zero Defects strategy can be depicted with the diagram as shown in Figure 2 below which describes, from a Quality Management point of view, the elements of such a program.

Figure 2: Zero Defects Framework – Functional / Process Flow

#### 2. APPLICATION OF THE ZERO DEFECTS FRAMEWORK

#### 2.1. General

This framework provides a set of established tools that semiconductor Suppliers can utilize for detecting, reducing and eliminating defects as part of their product and service offering. Semiconductor Users may specify certain tools as their expectations in agreement with Suppliers.

The selection of framework elements for combinations of a Supplier part and a User application depends on various considerations. They may include effectiveness, ease of use, availability, training, results and costs.

Table 3 lists several ZD framework elements that can be used for the following specific cases:

- Case 1: new product design in technology under development

- Case 2: new product design on automotive qualified technology

- Case 3: new product design on non-automotive qualified technology

- Case 4: released non-automotive product designated by supplier for automotive application

The template in Table 5 (refer to Section 9) can be used to communicate and document the strategy towards Zero Defects (ZD) for a given semiconductor product.

The ZD framework is built upon 6 pillars: Design, Manufacturing, Test, Application and Applicability, Continuous Improvement Methods, and Problem Solving, as reflected by the chapter structure of this

**Component Technical Committee**

document. Each pillar consists of methods and tools proposed to help in the following realms: description, relation to product life cycle, application and relevance, limitations and exceptions, metric and meaning of values, and references; and in some case examples. Organizations may consider applying elements in this framework, as they fit or use others that are not listed, based on the needs in that situation. In addition, all methods and tools in this document are a proposed set to help users navigate their projects, but they are not all inclusive for every situation.

AEC-Q004-001 (to be published) provides further details on how the elements of the ZD framework can be applied.

#### 2.2. Safe Launch

One of the best practices is implementation of Safe Launch plan during the ramp to production phase. The Safe Launch plan can be defined by either the Supplier or the User based on their determination of risk for product introduction. Safe Launch plan uses several tools already included in this ZD Framework document. For example, Suppliers could use Table 3 of this document when asked to support a User Safe Launch initiative (which also can be communicated by using Table 5).

#### 2.3. Cost Benefit Analysis

For some methods and tools, the supplier may have (including cases when products move from other applications/market areas into automotive) already factored in a cost/benefit analysis upon entering the automotive market. For example, the application of FMEAs, Control Plans, MSA studies, PAT, etc. is an inherent part of doing business in automotive. Therefore, these sections do not include a cost/benefit description. Though not all inclusive, cost/benefit considerations are described for methods and tools where measurable investment may be required for effective implementation.

Suppliers may need to do a cost/benefit analysis for planning and executing a Safe Launch initiative.

**Component Technical Committee**

### Table 3: Zero Defects Framework and Recommendations

Explanation: R = Recommended, U = Useful (and to be considered), N = Not applicable (or not useful)

Clarification: "Design" includes electrical circuitry and package construction / materials

|         |                |         |                                                                      |                       |        |        | Remarks                                                                                                                                                                                                                                                                                                 |

|---------|----------------|---------|----------------------------------------------------------------------|-----------------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter | Subject        | Section | ΤοοΙ                                                                 | Case 1<br>&<br>Case 2 | Case 3 | Case 4 | <ol> <li>New product design in technology under development</li> <li>New product design on automotive qualified technology</li> <li>New product design on non-automotive qualified technology</li> <li>Released non-automotive product designated by supplier for<br/>automotive application</li> </ol> |

|         |                | 3.1     | Design FMEA                                                          | R                     | R      | U      | Case 4: design risk review/assessment recommended to find potential<br>weaknesses in relation to the automotive application that may need<br>other actions than re-design                                                                                                                               |

|         |                | 3.2     | Redundancy                                                           | U                     | U      | N      | Case 4: redundancy at system level may have to be considered                                                                                                                                                                                                                                            |

|         |                | 3.3     | Built-in Self-Test (1)                                               | R                     | R      | N      | Case 4: if it was not considered before, there is no added value                                                                                                                                                                                                                                        |

|         |                | 3.4     | Design for Test (1)                                                  | R                     | R      | N      | Case 4: if it was not considered before, there is no added value;<br>unless it can be done via software solutions                                                                                                                                                                                       |

|         |                | 3.5     | Design for Analysis (1)                                              | R                     | R      | N      | Case 4: if it was not considered before, there is no added value                                                                                                                                                                                                                                        |

| 3       | Product Design | 3.6     | Design for Manufacture                                               | R                     | R      | N      | Case 4: if it was not considered before, there is no added value                                                                                                                                                                                                                                        |

|         |                | 3.7     | Design for Reliability                                               | R                     | R      | N      | Case 4: if it was not considered before, there is no added value:<br>reliability assessment recommended to find potential weaknesses in<br>relation to the automotive application that may need other actions<br>than re-design; other tools become more important                                      |

|         |                | 3.8     | Simulation and Modeling                                              | R                     | R      | U      | Case 4: based on re-specification (aging) simulation can reveal potential weakness mentioned under 3.7; other tools can be used to overcome this                                                                                                                                                        |

|         |                | 3.9     | Characterization                                                     | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

|         |                | 4.1     | Process FMEA                                                         | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

|         | Manufacturing  | 4.2     | Statistical Analysis of Variance                                     | U                     | U      | U      |                                                                                                                                                                                                                                                                                                         |

|         |                | 4.3     | Control Plan                                                         | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

| 4       |                | 4.4     | Statistical Process Control                                          | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

| 4       |                | 4.5     | Lot Acceptance Gates                                                 | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

|         |                | 4.6     | Audits (Management System,<br>Manufacturing Process, and<br>Product) | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

|         | Test           | 5.1     | Part Average Testing                                                 | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

|         |                | 5.2     | Statistical Bin Yield Analysis                                       | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

| 5       |                | 5.3     | Data Collection, Storage and Retrieval                               | R                     | R      | R      | Retention period to be agreed between User and Supplier                                                                                                                                                                                                                                                 |

|         |                | 5.4     | Screens                                                              | R                     | R      | R      |                                                                                                                                                                                                                                                                                                         |

## Automotive Electronics Council ------

**Component Technical Committee**

|         |                               |         |                                     |                       |        |        | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------|---------|-------------------------------------|-----------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter | Subject                       | Section | Tool                                | Case 1<br>&<br>Case 2 | Case 3 | Case 4 | <ol> <li>New product design in technology under development</li> <li>New product design on automotive qualified technology</li> <li>New product design on non-automotive qualified technology</li> <li>Released non-automotive product as designated by supplier,<br/>for automotive application</li> </ol>                                                                                                                                    |

|         | Application and<br>Capability | 6.1     | Industry Standards                  | R                     | R      | R      | Case 1: only if an existing standard is covering the new technology; if<br>not agreement between Supplier and User is leading (a standard<br>under development may be guideline)<br>Case 3, 4: in case the automotive standard cannot be met an<br>agreement between Supplier and User is needed how to deal with the<br>gap                                                                                                                   |

| 6       |                               | 6.2     | Environmental Stress Testing        | R                     | R      | R      | Case 1: only if an existing tests and requirements are covering the<br>new technology; if not agreement between Supplier and User is<br>leading (a standard under development may be guideline)<br>Case 3, 4: in case requirements cannot be met an agreement<br>between Supplier and User is needed how to deal with the gap<br>In all cases, it is best practice to use an agreed or even standardized<br>mission profile in this alignment) |

|         |                               | 6.3     | Stress-Strength Analysis            | R                     | R      | U      | Case 4: stress-strength assessment considered useful to find<br>potential weaknesses in relation to the automotive application that<br>may need other actions than re-design; other tools become more<br>important                                                                                                                                                                                                                             |

|         |                               | 6.4     | Systems Engineering                 | U                     | U      | N      | Case 1,2, 3: only for non-commodities. If applicable: under the condition that it is clear what can be "engineered" still to achieve zero defect<br>Case 4: assess the potential risks on defects from a system perspective and what can be done to mitigate (not applicable to commodities)                                                                                                                                                   |

|         |                               | 6.5     | Product Derating                    | U                     | U      | U      | Based on agreement between Supplier and User for the specific application conditions and parameters                                                                                                                                                                                                                                                                                                                                            |

|         | Improvement                   | 7.1     | Wafer Level Process Monitoring      | R                     | U      | U      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7       |                               | 7.2     | Process and Product<br>Improvements | R                     | R      | R      | PCN process to follow for major changes                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                               | 7.3     | Product Reliability Monitoring      | R                     | R      | R      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                               | 7.4     | Defect Monitoring                   | R                     | R      | R      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8       | Problem Solving               | 8.1     | Problem Solving Techniques          | R                     | R      | R      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ŭ       | 1 Iobioin Colving             | 8.2     | Failure Analysis Process            | R                     | R      | R      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Component Technical Committee**

#### 3. PRODUCT DESIGN

#### 3.1. Design Failure Mode and Effect Analysis (DFMEA)

#### 3.1.1. Description

DFMEA is a process performed by subject experts that identifies potential failure modes and their effects on the product in the system and its application, estimates their severity, occurrence and detection, and identifies possible causes and controls. The DFMEA document identifies the risks associated with something potentially going wrong (i.e., out of specification condition or loss of functionality) in the design of the product. The FMEA identifies what controls are placed in the design process to catch abnormal conditions with known or potential impact on specification or functionality of the product at various stages on the product development. The DFMEA provides a relative ranking (action priority) based on the risk and effect associated with the severity, occurrence and detection of a particular failure mode that facilitates prioritization of resources in implementation of controls in the design process. In summary, the DFMEA is essentially a collection of expert knowledge and lessons learned from other related processes and products.

#### 3.1.2. Relation to Product Life Cycle

DFMEAs are performed on all new components and systems during design of the product or development and implementation of process flow. DFMEA documents are also updated for all design changes. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.

#### 3.1.3. Application and Relevance

DFMEAs identify all known potential modes of failure in design, their risks and effects, and how to control them.

#### 3.1.4. Limitations and Exceptions

DFMEA is not applicable to a product that is either fully mature and not changed, or replaced, or discontinued (reaching End-of-Life).

#### 3.1.5. Metrics and Meaning of Values

Action Priority (AP) used to prioritize which failure mode or mechanism is most influential to product failure.

#### 3.1.6. References

- AIAG & VDA: FMEA Handbook

- JEP131: Process Failure Modes & Effects Analysis

**Component Technical Committee**

#### 3.2. Redundancy

#### 3.2.1. Description

A parallel system of duplicate cells or components that produces the same functionality and deliver equal performance to replace faulty ones seamlessly during the final test or actual use of a product. Redundancy can greatly increase the system's mean time to failure.

There are four predominant types of redundancy in electronics:

- 1. Hardware redundancy, such as dual modular redundancy and triple modular redundancy.

- 2. Information or automated redundancy, such as error detection and correction methods.

- 3. Time redundancy, performing the same operation multiple times such as multiple executions of a program or multiple copies of data transmitted.

- 4. Software redundancy such as N-version programming.

The type of redundancy is usually done during the product design phase and, therefore, the trade-off between the added cost of implementation and the benefit to the User has already been considered.

#### 3.2.2. Relation to Product Life Cycle

Used during design and test of semiconductor products.

#### 3.2.3. Application and Relevance

Greatly reduces failure rates via robust design (transparent cell replacement) and may reduce both 0 km and field failure rates. Use for critical memory and application functions or when die size percentage increase is small or low cost vs. benefit.

#### 3.2.4. Limitations and Exceptions

Certain design or performance restrictions may inhibit the use of redundancy.

#### 3.2.5. Metrics and Meaning of Values

System (or aggregate part) yield and number of Customer returns with measurement of instances where redundancy is observed, activated and recorded.

#### 3.2.6. References

- *Review on Redundancy in Electronics*, Mr. Gurudatt Kulkarni and Prof. Mrs. Lalita Wani. International Journal of Engineering and Computer Science, Nov 2013

- ISO26262, Road vehicles Functional safety

**Component Technical Committee**

#### 3.3. Built-in Self-Test

#### 3.3.1. Description

Built-in Self-Test, or BIST, is the practice of designing the circuitry such that inputting a logic solution will allow the product to test itself. It is a technique of designing additional hardware and software features into integrated circuits to allow them to perform self-testing. This involves testing of their own operation (functionally, parametrically, or both) using their own circuits, thereby reducing dependence on an external automated test equipment (ATE). BIST is a Design-for-Testability (DfT) technique because it makes the electrical testing of a product easier, faster, more efficient, and less costly. Examples of BIST functions can include checkerboard and inverse scan algorithms to detect bit-to-bit shorts and back-to-back reads, address decoder fault algorithms to check for speed fault, SRAM and NVM bitmapping, etc.

Issues that need to be considered when implementing BIST are: 1) faults to be covered by the BIST and how these will be tested for; 2) how much chip area will be occupied by the BIST circuits; 3) external supply and excitation requirements of the BIST; 4) test time and effectiveness of the BIST; 5) flexibility and changeability of the BIST (i.e., can the BIST be reprogrammed through an on-chip ROM?); 6) how the BIST will impact the production electrical test processes that are already in place.

Advantages of implementing BIST include:

- 1. Lower cost of test, since the need for external electrical testing using an ATE will be reduced, if not eliminated.

- 2. Better fault coverage, since special test structures can be incorporated onto the product.

- 3. Shorter test times if the BIST can be designed to test more structures in parallel.

- 4. Easier Customer support.

- 5. In exceptional cases, e.g., as part of a safety concept: capability to perform tests outside the production electrical testing environment; which may allow the consumers themselves to test the product prior to mounting or even after these are in the application boards.

Disadvantages of implementing BIST include:

- 1. Additional silicon area for the BIST circuits.

- 2. Reduced access times.

- 3. Additional pin (and possibly bigger package size) requirements, since the BIST circuitry need a way to interface with the outside world to be effective.

- 4. Possible issues with the correctness of BIST results, since the on-chip testing hardware itself can fail.

#### 3.3.2. Relation to Product Life Cycle

Built-in Self-Test is designed into the product and used during electrical test.

#### 3.3.3. Application and Relevance

Intended for use with high complexity products. Provides the product with the capability of diagnosing itself for processing errors both in development stage and in mass production. It may also address design errors that are detectable by functions or parameters internal to the product but not accessible from the outside.

#### 3.3.4. Limitations and Exceptions

Not intended for use with low complexity products. May be possible to switch off and not use as the part and process matures. May increase die size and software code.

## Automotive Electronics Council — Component Technical Committee

#### 3.3.5. Metrics and Meaning of Values

Defect detectability and test coverage.

#### 3.3.6. References

None.

**Component Technical Committee**

#### 3.4. Design for Test

#### 3.4.1. Description

The practice of designing the circuitry such that as many nodes as possible can be tested in a reasonable amount of time. Test plan reviews should be conducted to ensure maximum test coverage efficiency. Additional circuitry increases test efficiency by allowing for ability to accelerate a test stress to the element or circuit. In addition, design for test can improve fault coverage by allowing direct access to and control of circuits or elements embedded within the product that cannot be accessed directly through the I/Os. Direct access can also provide ability to better observe the result or impact of the test.

Examples of DfT can include: fault coverage of scan stuck-at and transition faults (AC scan: fault delay tests, transition delay tests, coupling faults), critical timing paths from static timing analysis, functional/speed patterns to test I/O interface, analog I/O patterns for voltage ramps and DC tests, drive strength and slew rates, and Customer application codes (User and Supplier).

Costs may include layout complexity, potential design time increase, and test software development. Benefits may include more efficient defect screening.

#### 3.4.2. Relation to Product Life Cycle

Design for Test can be applied by Supplier and User.

#### 3.4.3. Application and Relevance

Intended for use with high complexity products. Provides the capability for testing as many nodes as possible and, thus, providing maximum fault coverage during test.

#### 3.4.4. Limitations and Exceptions

Not intended for use with low complexity products.

#### 3.4.5. Metrics and Meaning of Values

Test coverage, reduced incidence of NTF/TNI, and improved cycle time.

#### 3.4.6. References

AEC-Q100-007: Fault Simulation and Fault Grading

#### 3.4.7. Examples

Examples include selecting multiple memory array columns during a stress or directly accessing a memory cell to measure the Vt (threshold voltage) of the cell.

Example of a design and test program:

- 1. Use of Geometric Dimensioning and Tolerancing (GD&T) to provide unambiguous representation of design intent (refer also to Section 3.6.7).

- 2. Specification of product parameters and tolerances that are within the natural capabilities of the manufacturing process (process capability index Cp and Cpk) (refer also to Section 3.6.7).

- 3. Provision of test points, access to test points and connections, and sufficient real estate to support test points, connections, and built-in test capabilities.

- 4. Standard connections and interfaces to facilitate use of standard test equipment and connectors and to reduce effort to setup and connect the product during testing.

- 5. Automated test equipment compatibility.

## Automotive Electronics Council — Component Technical Committee

- 6. Built-in test and diagnosis capability to provide self-test and self-diagnosis in the factory and in the field.

- 7. Physical and electrical partitioning to facilitate test and isolation of faults.

**Component Technical Committee**

#### 3.5. Design for Analysis

#### 3.5.1. Description

The practice of designing the circuitry such that failure analysis can be performed as efficiently as possible for elimination of no defect found. These design considerations include modes that allow direct control and observation of embedded circuitry or elements to better electrically isolate the failing circuitry. In addition, for multiple metal layer technologies, probe points can provide access to embedded circuitry or underlying layers for control during physical failure analysis.

Costs may include layout complexity and potential design time increase. Benefits may include easier and more efficient failure analysis.

#### 3.5.2. Relation to Product Life Cycle

Intended for use with all designs having a large number of metal layers or unique interconnection schemes (e.g., chip-on-chip).

#### 3.5.3. Application and Relevance

Intended for use with high complexity products. Provides the capability of a more accurate and accessible analysis of failures which otherwise could be inaccessible either electrically or physically.

#### 3.5.4. Limitations and Exceptions

Not intended for use with low complexity products (few metal levels). If the product offers security features, this may limit the ability to design those features for analysis.

#### 3.5.5. Metrics and Meaning of Values

Reduced cycle time for Failure Analysis (FA) and reduced incidence of TNI.

#### 3.5.6. References

None.

**Component Technical Committee**

#### 3.6. Design for Manufacturability

#### 3.6.1. Description

The practice of designing the circuitry so that manufacturing of the part is more repeatable and reproducible via larger design margins. These designs are intended to reduce the effects of extrinsic defects on the device, such as particles and process margins (e.g., lithography definition).

Costs may include increased die area to accommodate design margin techniques (e.g., redundant vias, etc.). Benefits may include reduced manufacturing defects and increased yield.

#### 3.6.2. Relation to Product Life Cycle

Intended for use in new processes or sub-processes, new technology, new material sets or subsets and new fab or assembly sites. Implemented in the design of the product.

#### 3.6.3. Application and Relevance

Design for manufacturability reduces the impact of extrinsic defects on product yield and quality.

#### 3.6.4. Limitations and Exceptions

None.

#### 3.6.5. Metrics and Meaning of Values

Manufacturing yield, process control improvement.

#### 3.6.6. References

None.

#### 3.6.7. Examples

Examples include:

- 1. Doubling (redundant) vias in areas that are process sensitive (e.g., sparse areas of vias), widening spacing between interconnect lines.

- 2. Reducing the number of critical timing paths using synthesis tools.

- 3. Usage of Geometric Dimensioning and Tolerancing (GD&T) to provide unambiguous representation of design intent (refer also to Section 3.4.6).

- 4. Specification of product parameters and tolerances that are within the natural capabilities of the manufacturing process (process capability index Cp and Cpk) (refer also to Section 3.4.6).

**Component Technical Committee**

#### 3.7. Design for Reliability

#### 3.7.1. Description

Design for Reliability (DfR) summarizes the efforts within the development process to design products that do not wear out during the entire life of the product where used as specified. This requires a systematic design approach based on awareness and consideration of the real use and accurate application of Physics-of-Failure (PoF). DfR uses a wide range of tools supporting design rules and product and process design, including but not limited to: material selection, computer-aided engineering (CAE) analysis and simulation tools, redundancy in design (e.g., redundant via in metallization) and physical characterization.

Design for reliability can provide the capability to measure and predict product reliability lifetime. Reliability issues can be prevented by designing in margin to the circuit, layout, or construction without sacrificing performance. Silicon level reliability can be monitored by test structures designed into the device or sawing lanes.

Design of Experiments techniques can provide a structured, proactive approach to improving reliability and robustness as compared to unstructured, reactive design/build/test approaches. This is done by understanding the effects of both product and process parameters on the reliability of the product and address the effect of interactions between parameters. From that, the development and use of computer-aided engineering (CAE) analysis and simulation tools at an early stage in the design process can improve product reliability more inexpensively and in a shorter time than building and testing physical prototypes. Examples of processes that DfR can utilize include finite element analysis, fluid flow analysis, thermal analysis and PoF-based.

Costs may include increase die size during development phase. Benefits may include lower risk of fails during later development and in qualification, and of need for late design revisions. Risk for field failures could also be reduced.

#### 3.7.2. Relation to Product Life Cycle

DfR approach is most effective if applied from early concept phase on throughout the whole development process. It is intended for use in any kind of design / development / change of parts, technologies / processes or in the consideration process of products for new applications.

#### 3.7.3. Application and Relevance

The described approach is applicable in development in general for IPs, libraries, components, and technologies for wafer and package.

#### 3.7.4. Limitations and Exceptions

No limitations, but more applicable for high complexity products.

#### 3.7.5. Metrics and Meaning of Values

Lifetime, failure probability, failure rate.

#### 3.7.6. References

- JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments

- SAE J1211 Robustness Validation for Electrical/Electronic Modules Section 8 Modeling Analysis and Simulation

- SAE ARP6338 Process for Assessment and Mitigation of Early Wear-out of Life-Limited Microcircuits

**Component Technical Committee**

#### 3.7.7. Examples

- 1. Design based on the specified range of the operating environment (e.g., product is used in a passenger compartment environment vs. engine management).

- 2. Design to minimize or balance stresses and thermal loads (Optimization of multiple wire bonds of power stage to homogenize the temperature distribution).

- 3. Add margin in design (e.g., scale-up; increase metal trace width).

- 4. Provide subsystem redundancy (e.g., double via).

- 5. Error correction (e.g., NVM, Soft error detection and correction, data retention margins).

- 6. Use proven elements, materials, IPs & libraries with well-characterized reliability (e.g., reuse of proven I/O cells).

- 7. Consolidate the number of design elements & interconnections to reduce their failure opportunities.

**Component Technical Committee**

#### 3.8. Simulation and Modeling

#### 3.8.1. Description

Simulation is a method to model the device functionality and reliability performance of the finished product or part of it, which uses process element models, package physical and materials models, and design guidelines to validate the product functionality and performance over lifetime.

With increasing complexity and diversity of silicon-based semiconductor products, it becomes virtually unworkable to verify reliability with only stress experiments on products. Simulations can provide orders of magnitude larger parametric variation than validation on actual products only (provided that the technology supports the reliability models). This is due to being able to setup worst case conditions for multiple fail modes for mission profiles.

Costs may include addition of resources for simulation program development or purchase and data analysis. Benefits may include mitigating defects in design that otherwise would promulgate to manufacturing.

#### 3.8.2. Relation to Product Life Cycle

Performed on all products during the design phase and possibly during the evaluation phase. May be used during production to aid in debug or Failure Analysis (FA). Simulation should always be used for every significant silicon pass.

#### 3.8.3. Application and Relevance

Verifies functional operation of the product in addition to highlighting process, voltage and temperature sensitivities related directly to the design and process parametric behavior including margins.

#### 3.8.4. Limitations and Exceptions

In general, not intended for use after the product has been ramped up to full production (i.e., after initial release of the product), except to support Failure Analysis (FA) in some cases.

#### 3.8.5. Metrics and Meaning of Values

Direct simulation of specified parameters, functions and margins, parameter fit to empirical data, confidence bounds, fault coverage values, coverage of requirements and other appropriate metrics.

#### 3.8.6. References

- AEC-Q100-007: Fault Simulation and Fault Grading

- JEP122: Failure Mechanisms and Models for Silicon Semiconductor Devices

- JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments

- SAE J3083 Reliability Prediction for Automotive Electronics Based on Field Return Data

#### 3.8.7. Examples

Illustrations of device validation coverage challenges, where simulation can add confidence/coverage:

• Electro-migration (EM) cannot be sufficiently accelerated in HTOL to achieve end of life. EM is driven by current and temperature. By the time the temperature objective is reached for equivalent EOL stress, other mechanisms have far exceeded the end of life (i.e., TDDB and BTI).

**Component Technical Committee**