# **DRAFT**

**AEC - Q004** August 31, 2006

# ZERO DEFECTS GUIDELINE

**AMRDEC**

**AMRDEC**

# **Automotive Electronics Council**

**Component Technical Committee**

# Acknowledgment

Any document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:

> **Guest Members: David Locker**

Jeff Jarvis

Sustaining Members:

Mark A. Kelly Delphi Corporation Siemens VDO Jean Clarac Brian Jendro Siemens VDO Robert V. Knoell Visteon Corporation

**Associate Members:**

Tim Haifley Altera

Daniel Vanderstraeten **AMI Semiconductor**

Earl Fischer Autoliv Mike Klucher Cirrus Logic Xin Miao Zhao Cirrus Logic

John Timms Continental Automotive Systems Roy Ozark Continental Automotive Systems

Nick Lycoudes Freescale

Werner Kanert Infineon Technologies Infineon Technologies Elfriede Geyer John Bertaux International Rectifier Gary Fisher Johnson Controls Tom Lawler Lattice Semiconductor

Mike Buzinski Microchip Rob Horton Microchip **NEC Electronics** Annette Nettles Raj Radjassamy **NEC Electronics Zhongning Liang NXP Semiconductors** Mark Gabrielle ON Semiconductor Ken Berry Renesas Technology

Bruce Townsend Spansion Adam Fogle Spansion

Brian Mielewski **STMicroelectronics** James Williams **Texas Instruments** Diana Siddall **Texas Instruments**

Don Pecko Xilinx

Other Contributors:

**NEC Electronics** Masachi Murase Michael Wieberneit **NEC Electronics**

David Lehtonen Spansion

**Component Technical Committee**

#### NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.

AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.

AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in Conformance with this document shall be made unless all requirements stated in the document are met.

Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link http://www.aecouncil.com.

Published by the Automotive Electronics Council.

This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

Printed in the U.S.A. All rights reserved

Copyright © 2006 by Delphi, Siemens VDO, and Visteon Corporation. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.

**Component Technical Committee**

## ZERO DEFECTS GUIDELINE

The proposed DRAFT of AEC-Q004 is made available for a 6-month industry review period, scheduled to expire on April 1, 2007. All comments and suggested edits should be made by contacting the AEC Technical Committee (http://www.aecouncil.com/AECRequest.html). After the 6-month review period has expired, all received comments and suggestions will be reviewed by the Technical Committee and incorporated (where applicable) into a final version of the Q004 document.

#### 1. SCOPE

This document describes and organizes a set of tools and processes which suppliers and users of integrated circuits can use to approach or achieve the goal of zero defects during a product's lifetime. This guideline makes suggestions for when each of these tools and methods should be used depending on the application or business case.

This is not to be construed as a requirements document, but is a tool box of methods that have been used to reduce defects. This is not an exhaustive list. There are suppliers that are using internally developed and proprietary methods to reduce defects. As the part and/or process is optimized and matures over time, less tools are needed to improve or maintain quality and reliability.

# 1.1 Purpose

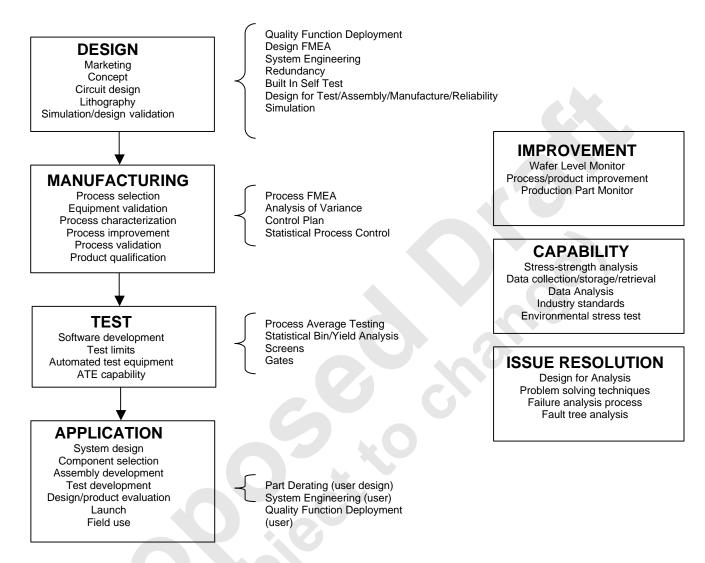

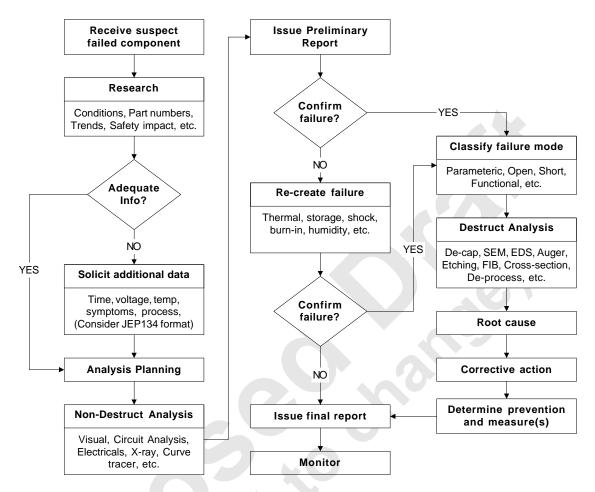

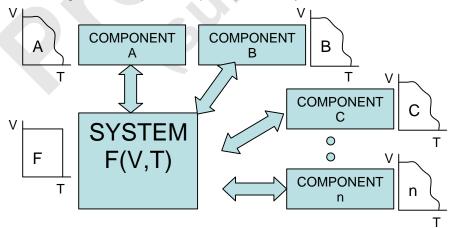

The flowchart below describes the sequence of steps involved in component design, manufacture, test and use and where each of the zero defect tool or method fits in with this component flow. Each tool or method is described along with how it addresses zero defects, when it would or wouldn't be used, the estimated cost versus benefit, the components and technologies it applies to, the defect type addressed and the metric used to measure performance.

**Component Technical Committee**

Figure 1: Zero Defects Flow

**Component Technical Committee**

# 1.2 Reference Documents

- AEC-Q100: Stress Test Qualification for Integrated Circuits

- AEC-Q101: Stress Test Qualification for Discrete Semiconductors

- AEC-Q100-009: Electrical Distribution Assessment

- AEC-Q001: Guidelines for Part Average Testing

- AEC-Q002: Guidelines for Statistical Yield Analysis

- APQP-2: Advanced Product Quality Planning & Control Plan

- EIA 659: Failure Mechanism Driven Reliability Monitoring

- EIA-557-A: Statistical Process Control Systems

- FMEA-3: Potential Failure Modes & Effects Analysis, AIAG

- JESD50A: Special Requirements for Maverick Product Elimination

- JEP13A: Guideline for Constant Temperature Aging to Characterize Aluminum Interconnect Method for Stress Migration Induced Voiding

- JEP119A: A Procedure For Executing SWEAT

- JEP122B: Failure Mechanisms and Models for Silicon Semiconductor Devices

- JEP131A: Process Failure Modes & Effects Analysis

- JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments

- JEP150: Stress Test Drive Qualification of and Failure Mechanisms Associated With Assembled Solid State Surface Mount Components

- JESD16-a: Assessment of Average Outgoing Quality Levels in Parts Per Million (PPM)

- JESD35: Procedure for Wafer Level Testing of Thin Dielectrics

- JESD671: Component Quality Problem Analysis and Corrective Action Requirements

- JESD74: Early Life Failure Rate Calculation Procedure for Electronic Components

- JESD94: Application Specific Qualification Using Knowledge Based Test Methodology

- JESD659: Failure Mechanism Driven Reliability Monitoring

- SPC-3: Statistical Process Control, AIAG

- JEDEC JESD-46 Customer Notification of Product/Process Changes by Semiconductor Suppliers

**Component Technical Committee**

# **LIST OF REFERENCES**

| Sect# | Tool                                     | AEC                              | JEDEC                      | AIAG   | SAE | IEC | Other                                |

|-------|------------------------------------------|----------------------------------|----------------------------|--------|-----|-----|--------------------------------------|

| 3.1   | Failure Mode and Effect                  |                                  |                            | FMEA-3 |     |     |                                      |

| 4.1   | Analysis (FMEA)                          |                                  |                            | JEP131 |     |     |                                      |

| 3.2   | Redundancy                               |                                  |                            |        |     |     |                                      |

| 3.3   | Built-in Self Test                       |                                  |                            |        |     |     |                                      |

| 5.2   |                                          |                                  |                            |        |     |     |                                      |

| 3.4   | Design for Test                          |                                  |                            |        |     |     |                                      |

| 5.1   |                                          |                                  |                            |        |     |     |                                      |

| 3.5   | Design for Analysis                      |                                  |                            |        |     |     |                                      |

| 8.1   |                                          |                                  |                            |        |     |     |                                      |

| 3.6   | Design for Manufacture                   |                                  |                            |        |     |     |                                      |

| 3.7   | Design for Reliability                   |                                  | JEP148                     |        |     |     |                                      |

| 3.8   | Simulation                               |                                  | JEP122<br>JEP148           |        |     |     |                                      |

| 3.9   | Characterization                         | AEC-Q003<br>AEC-Q100-<br>009     |                            |        |     |     |                                      |

| 4.2   | Statistical Analysis of Variance         |                                  |                            |        |     | 01  |                                      |

| 4.3   | Control Plan                             |                                  |                            | APQP-2 |     |     |                                      |

| 4.4   | Statistical Process Control              |                                  | EIA557                     | SPC-3  |     |     |                                      |

| 5.3   | Process/Part Average Testing             | AEC-Q001                         |                            |        |     |     |                                      |

| 5.4   | Statistical Bin Yield Analysis           | AEC-Q002                         |                            | . 7    |     |     |                                      |

| 5.5   | Data Collection, Storage and Retrieval   |                                  |                            |        |     |     |                                      |

| 5.6   | Screens                                  | JESD50<br>JESD16<br>JESD74       |                            | 0,     |     |     | MIL-PRF-<br>19500<br>MIL-STD-<br>883 |

| 5.7   | Lot Acceptance Gates                     | JESD50<br>JESD16<br>JESD74       |                            |        |     |     |                                      |

| 6.1   | Stress-Strength Analysis                 |                                  |                            |        |     |     |                                      |

| 6.2   | Data Analysis                            |                                  |                            |        |     |     |                                      |

| 6.3   | Industry Standards                       |                                  |                            |        |     |     |                                      |

| 6.4   | Environmental Stress Testing             | AEC-Q100<br>AEC-Q101<br>AEC-Q200 | JESD22<br>JESD94<br>JEP150 |        |     |     |                                      |

| 6.5   | Part Derating                            |                                  |                            |        |     |     |                                      |

| 7.1   | Wafer Level Failure Mechanism Monitoring |                                  |                            |        |     |     |                                      |

| 7.2   | Process/Product<br>Improvements          | AEC-Q100                         | JESD46                     |        |     |     |                                      |

| 7.3   | Production Part Monitoring               |                                  | EIA/JESD659                |        |     |     |                                      |

| 8.2   | Problem Solving Techniques               |                                  | JESD671                    |        |     |     |                                      |

| 8.3   | Failure Analysis Process                 |                                  | JESD671                    |        |     |     |                                      |

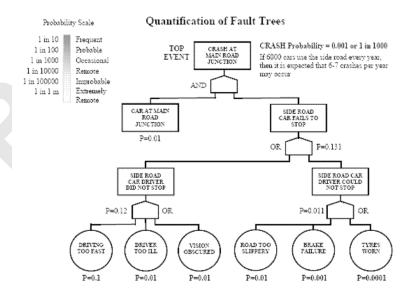

| 8.4   | Fault Tree Analysis                      |                                  |                            |        |     |     |                                      |

| 9.1   | System Engineering                       |                                  |                            |        |     |     |                                      |

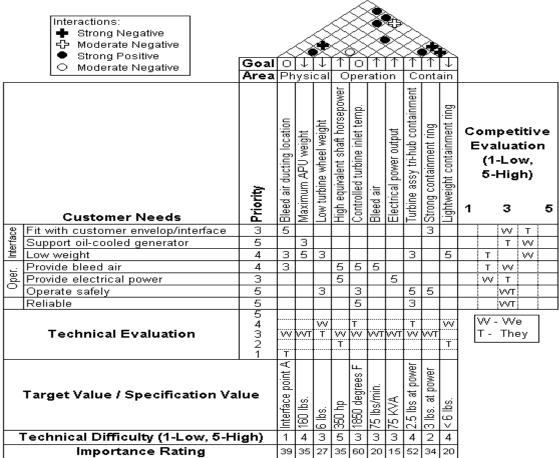

| 9.2   | Quality Function Deployment              |                                  |                            |        |     |     |                                      |

# 1.3 Definitions

Data mining – automating the process of searching for patterns in a data set. Ongoing defect – typically a common cause or intrinsic failure that follows a trend Spike defect – typically a special cause or extrinsic failure that occurs infrequently NTF – No trouble found

TNI - Trouble not identified

# Automotive Electronics Council Component Technical Committee

#### 2. **RECOMMENDATIONS**

✓ recommended/needed o may be used x not recommended/needed

|            |                                          |                                            |                            | nay be us                 |                                                     |                                             |                                   |                                  |                                   |                                                          |

|------------|------------------------------------------|--------------------------------------------|----------------------------|---------------------------|-----------------------------------------------------|---------------------------------------------|-----------------------------------|----------------------------------|-----------------------------------|----------------------------------------------------------|

| Sect       | Tool                                     | All new<br>parts at<br>the design<br>stage | High<br>complexity<br>part | Low<br>complexity<br>part | Fully mature<br>or near<br>obsolescent<br>component | Cost<br>sensitive<br>part or<br>application | Design<br>or<br>process<br>change | Issue<br>or<br>failure<br>occurs | Low<br>reliability<br>application | High reliability<br>or safety<br>critical<br>application |

| 3.1<br>4.1 | Failure Mode and Effect<br>Analysis FMEA | <b>√</b>                                   | 0                          | ×                         | ×                                                   | 0                                           | <b>√</b>                          | ✓                                | ×                                 | ✓                                                        |

| 3.2        | Redundancy                               | 0                                          | <b>√</b>                   | ×                         | ×                                                   | ×                                           | ×                                 | ×                                | ×                                 | ✓                                                        |

| 3.3<br>5.2 | Built-in Self Test                       | 0                                          | <b>√</b>                   | ×                         | ×                                                   | ×                                           | ×                                 | <b>√</b>                         | ×                                 | ✓ <b>✓</b>                                               |

| 3.4<br>5.1 | Design for Test                          | ✓                                          | ✓                          | ×                         | ×                                                   | ×                                           | ✓                                 | $\checkmark$                     | ×                                 | <b>√</b>                                                 |

| 3.5<br>8.1 | Design for Analysis                      | 0                                          | ✓                          | ×                         | 0                                                   | ×                                           | 0                                 | <b>V</b>                         | ×                                 | ✓                                                        |

| 3.6        | Design for Manufacture                   | 0                                          | 0                          | ×                         | ×                                                   | 0                                           | $\checkmark$                      | $\checkmark$                     | ×                                 | ✓                                                        |

| 3.7        | Design for Reliability                   | 0                                          | 0                          | ×                         | ×                                                   | 0                                           | 0                                 | <b>√</b>                         | ×                                 | ✓                                                        |

| 3.8        | Simulation                               | ✓                                          | $\checkmark$               | 0                         | 0                                                   | 1                                           | 0                                 | $\checkmark$                     | 0                                 | ✓                                                        |

| 3.9        | Characterization                         | <b>√</b>                                   | <b>√</b>                   | ×                         | ×                                                   | 0                                           | $\checkmark$                      | 0                                | ×                                 | <b>√</b>                                                 |

| 4.2        | Statistical Analysis of Variance         | 0                                          | 0                          | 0                         | ×                                                   | 0                                           | 0                                 | 1                                | 0                                 | 0                                                        |

| 4.3        | Control Plan                             | 0                                          | 0                          | 0                         | ×                                                   | 0                                           | <b>V</b>                          | 0                                | 0                                 | ✓                                                        |

| 4.4        | Statistical Process<br>Control           | <b>√</b>                                   | <b>√</b>                   | <b>√</b>                  | <b>V</b>                                            | $\checkmark$                                | $\checkmark$                      | <b>V</b>                         | <b>√</b>                          | <b>√</b>                                                 |

| 5.3        | Process/Part Average<br>Testing          | ✓                                          | 0                          | 0                         | x                                                   | 0                                           | 0                                 | 0                                | ×                                 | <b>√</b>                                                 |

| 5.4        | Statistical Bin Yield<br>Analysis        | <b>✓</b>                                   | 0                          | 0                         | ×                                                   | 0                                           | 0                                 | 0                                | ×                                 | <b>√</b>                                                 |

| 5.5        | Data Collection, Storage and Retrieval   | 0                                          | 0                          | 0                         | <b>✓</b>                                            | 0                                           | <b>√</b>                          | <b>√</b>                         | 0                                 | 0                                                        |

| 5.6        | Screens                                  | $\checkmark$                               | $\checkmark$               | $\checkmark$              | <b>✓</b>                                            | <b>✓</b>                                    | $\checkmark$                      | $\checkmark$                     | <b>✓</b>                          | $\checkmark$                                             |

| 5.7        | Lot Acceptance Gates                     | 0                                          | $\checkmark$               | 0                         | <b>V</b>                                            | <b>✓</b>                                    | 0                                 | 0                                | ✓                                 | 0                                                        |

| 6.1        | Stress-Strength Analysis                 | 0                                          | $\checkmark$               | 0                         | ×                                                   | ×                                           | 0                                 | X                                | ×                                 | ✓                                                        |

| 6.2        | Data Analysis                            | $\checkmark$                               | $\checkmark$               | $\checkmark$              | $\checkmark$                                        | ✓                                           | ✓                                 | ✓                                | ✓                                 | ✓                                                        |

| 6.3        | Industry Standards                       | $\checkmark$                               | <b>√</b>                   | $\checkmark$              | <b>√</b>                                            | ✓                                           | ✓                                 | <b>√</b>                         | <b>√</b>                          | <b>√</b>                                                 |

| 6.4        | Environmental Stress<br>Testing          | <b>V</b>                                   | <b>√</b>                   | 0                         | ×                                                   | 0                                           | <b>√</b>                          | 0                                | 0                                 | <b>√</b>                                                 |

| 6.5        | Part Derating                            | $\checkmark$                               | ×                          | <b>√</b>                  | ✓                                                   | 0                                           | 0                                 | ×                                | ✓                                 | ×                                                        |

| 7.1        | Wafer Level Fail<br>Mechanism Monitoring | <b>√</b>                                   | 0                          | 0                         | 0                                                   | ×                                           | 0                                 | 0                                | ×                                 | <b>√</b>                                                 |

| 7.2        | Process/Product<br>Improvements          | 0                                          | 0                          | 0                         | ×                                                   | ×                                           | <b>√</b>                          | <b>√</b>                         | 0                                 | <b>√</b>                                                 |

| 7.3        | Production Part<br>Monitoring            | 0                                          | 0                          | 0                         | ×                                                   | ×                                           | 0                                 | 0                                | ×                                 | <b>√</b>                                                 |

| 8.2        | Problem Solving<br>Techniques            | 0                                          | 0                          | 0                         | 0                                                   | 0                                           | ✓                                 | <b>√</b>                         | 0                                 | 0                                                        |

| 8.3        | Failure Analysis Process                 | 0                                          | 0                          | 0                         | 0                                                   | 0                                           | ✓                                 | ✓                                | 0                                 | 0                                                        |

| 8.4        | Fault Tree Analysis                      | 0                                          | 0                          | 0                         | 0                                                   | 0                                           | ✓                                 | <b>√</b>                         | 0                                 | 0                                                        |

| 9.1        | System Engineering                       | ✓                                          | 0                          | 0                         | ×                                                   | ×                                           | ×                                 | ×                                | ×                                 | 0                                                        |

| 9.2        | Quality Function<br>Deployment           | <b>√</b>                                   | 0                          | 0                         | ×                                                   | ×                                           | ×                                 | ×                                | ×                                 | 0                                                        |

**Component Technical Committee**

#### 3. DESIGN

# 3.1 Failure Mode and Effect Analysis (FMEA)

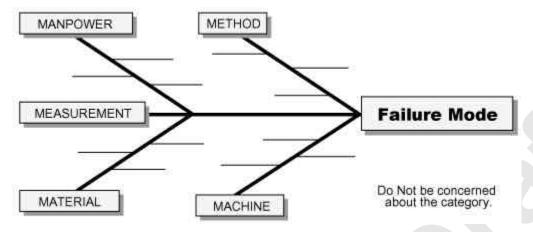

### 3.1.1 Description

A process performed by subject experts that identifies potential failure modes and their effects on the system and customer, determines their severity, occurrence and detection, and identifies possible causes and controls. The FMEA document identifies the risks associated with something potentially going wrong (creating a defect - out of specification) in the production of the product. The FMEA identifies what controls are placed in the production process to catch any defects at various stages on the processing. This applies both to process and design (product) FMEAs. The FMEA is essentially a collection of lessons learned from other related processes and products.

#### 3.1.2 Where this fits in the material flow

DFMEAs are performed on all new components and systems before design of component or arrangement of process flow. DFMEAs are also updated for all design changes. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.

# 3.1.3 Components and technologies this applies to and how it addresses zero defects

DFMEAs identify all potential modes of failure in design, their risks and how to control them.

## 3.1.4 Limitations

Not intended for use with a product that is fully mature or is entering obsoletion.

# 3.1.5 <u>Estimated cost versus benefit</u>

Cost includes man-hours to generate the expert knowledge document and uncertainty to new unknown failure mechanisms/modes. Benefit includes prioritizing the circuit or process step most susceptible to part failure in order to improve it and communicating learning throughout the organization.

# 3.1.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects based on lessons learned.

# 3.1.7 Metrics used and meaning of values

Risk priority number (product of severity, occurrence and detection) used to pareto which failure mode or mechanism is most influential to product failure.

#### 3.1.8 References

FMEA-3: Potential Failure Modes & Effects Analysis, AIAG

# 3.1.9 Examples

Example of a FMEA is shown in figure 4.1a

**Component Technical Committee**

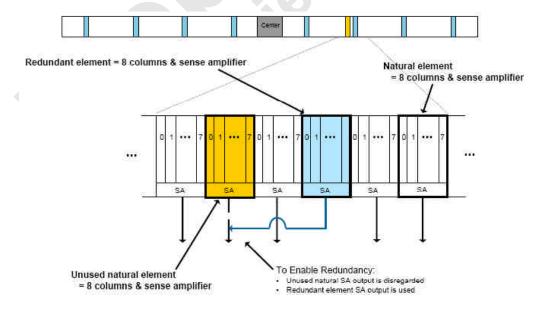

# 3.2 Redundancy

### 3.2.1 Description

A parallel system of duplicate cells or components that can replace faulty ones seamlessly during the final test or actual use of a part. Redundancy can greatly increase the part's mean time to failure. Another form of redundancy is error correction code to avoid latent data retention errors.

#### 3.2.2 Where this fits in the material flow

Used during design and test of logic, memory (e.g., flash, OTP), etc.

## 3.2.3 Components and technologies this applies to and how it addresses zero defects

Greatly reduces failure rates via robust design (transparent cell replacement), and may reduce both 0 km (time zero) and field failure rates. Use for critical memory and application functions or when die size percentage increase is small or low cost vs. benefit.

#### 3.2.4 Limitations

Design or performance restrictions may inhibit the use of redundancy. Not intended for use with low complexity or mature devices. Not to be used for low lifetime applications or where cost per die size is critical.

### 3.2.5 Estimated cost versus benefit

Cost includes added circuitry, overhead support, and software. Benefit includes much improved reliability.

# 3.2.6 <u>Defect type addressed (ongoing or spike)</u>

Both ongoing and spike defects.

### 3.2.7 Metrics used and meaning of values

Yield and number of customer returns.

### 3.2.8 References

# 3.2.9 Examples

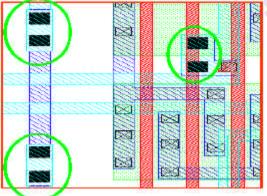

Example of redundancy in a memory array:

**Component Technical Committee**

# 3.3 Built-in Self Test

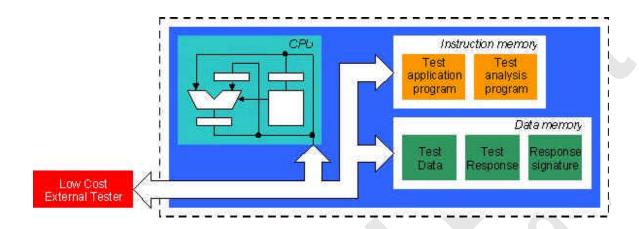

#### 3.3.1 Description

The practice of designing the circuitry such that inputting a logic solution will allow the part to test itself.

#### 3.3.2 Where this fits in the material flow

Intended for use with high complexity components and is designed into the product.

# 3.3.3 Components and technologies this applies to and how it addresses zero defects

Provides the device with the capability of diagnosing itself for process or design errors which otherwise might go undetected through the development stage. This includes functions or parametrics internal to the device that are not accessible from the outside.

#### 3.3.4 Limitations

Not intended for use with low complexity parts. May be possible to switch off and not use as the part and process matures. May increase die size and software code.

## 3.3.5 Estimated cost versus benefit

Cost includes added circuitry and software. Benefit includes improved fault coverage over the die.

# 3.3.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects.

#### 3.3.7 Metrics used and meaning of values

Defect detectability and test coverage

### 3.3.8 References

#### 3.3.9 Examples

Example of a BIST circuit block and test program is shown in figure 3.3a

**Component Technical Committee**

# 3.4 Design for Test

### 3.4.1 <u>Description</u>

The practice of designing the circuitry such that as many nodes as possible can be tested in a reasonable amount of time.

#### 3.4.2 Where this fits in the material flow

Intended for use with high complexity components and is designed into the product.

# 3.4.3 Components and technologies this applies to and how it addresses zero defects

Provides the capability for testing as many nodes as possible and, thus, providing maximum fault coverage during test.

## 3.4.4 Limitations

Not intended for use with low complexity parts.

#### 3.4.5 Estimated cost versus benefit

Cost includes layout complexity, potential design time increase, and test software development. Benefit includes more efficient defect screening.

# 3.4.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects.

# 3.4.7 Metrics used and meaning of values

Test coverage, reduced incidence of NPF/TNI, and improved cycle time.

#### 3.4.8 References

#### 3.4.9 Examples

Example of a test program with percent fault coverage and test time is shown in figure 3.4a

**Component Technical Committee**

# 3.5 Design for Analysis

### 3.5.1 <u>Description</u>

The practice of designing the circuitry such that failure analysis can be performed as efficiently as possible for elimination of no defect found.

#### 3.5.2 Where this fits in the material flow

Intended for use with all components having a large number of metal layers or unique interconnection schemes (e.g., chip-on-chip). Designed into the product.

# 3.5.3 Components and technologies this applies to and how it addresses zero defects

Provides the capability of a more accurate and accessible analysis of failures which otherwise could be masked by the proliferation of materials and features over the failed site.

#### 3.5.4 Limitations

Not intended for use with low complexity parts (few metal levels).

#### 3.5.5 Estimated cost versus benefit

Cost includes layout complexity and potential design time increase. Benefit includes easier and more efficient failure analysis.

# 3.5.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects.

#### 3.5.7 Metrics used and meaning of values

Reduced cycle time for FA and reduced incidence of NPF/TNI.

### 3.5.8 References

#### 3.5.9 Examples

Example of chip designs allowing for DFA is shown in figure 3.5a

**Component Technical Committee**

# 3.6 Design for Manufacture

### 3.6.1 <u>Description</u>

The practice of designing the circuitry so that the part can be more easily manufactured via larger design margins. These designs are intended to reduce the effects of extrinsic defects on the device, such as particulates and process margins (e.g., lithography definition).

# 3.6.2 Where this fits in the material flow

Intended for use in new processes or sub-processes, new technology, new material sets or subsets and new fab or assembly sites.

## 3.6.3 Components and technologies this applies to and how it addresses zero defects

Examples include doubling (redundant) vias in areas that are process sensitive (e.g., sparse areas of vias), widen spacing between interconnect lines, reduce the number of critical timing paths using synthesis tools.

#### 3.6.4 Limitations

Not intended for use in standard parts or processes and mature processes and technologies.

# 3.6.5 <u>Estimated cost versus benefit</u>

Cost includes increased die area to accommodate design margin techniques (e.g., redundant vias). Benefit includes reduced manufacturing defects (increased yield).

# 3.6.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects.

#### 3.6.7 Metrics used and meaning of values

Manufacturing yield, process control improvement

#### 3.6.8 References

# 3.6.9 Examples

Example of design margin for DFM is shown in figure 3.6a

Figure 3.6a - Redundant vias in place of isolated ones

**Component Technical Committee**

# 3.7 Design for Reliability

#### 3.7.1 <u>Description</u>

Relaxation of design rules without sacrificing performance. The use of physics of failure to determine design and material limitations. Use of computer-aided engineering (CAE) analysis and simulation tools at an early stage in the design can improve product reliability more inexpensively and in a shorter time than building and testing physical prototypes. Tools such as finite element analysis, fluid flow, thermal analysis, integrated reliability prediction models, etc., are becoming more widely used, more user friendly and less expensive. Design of Experiments techniques can provide a structured, proactive approach to improving reliability and robustness as compared to unstructured, reactive design/build/test approaches. Further, these techniques consider the effect of both product and process parameters on the reliability of the product and address the effect of interactions between parameters. Finally, the company should begin establishing a mechanism to accumulate and apply "lessons learned" from the past related to reliability problems as well as other producibility and maintainability issues. These lessons learned can be very useful in avoiding making the same mistakes twice.

#### 3.7.2 Where this fits in the material flow

Intended for use in new part designs or processes, parts designed for new applications, applications requiring high reliability.

# 3.7.3 Components and technologies this applies to and how it addresses zero defects

Provides the capability of more rapid evaluation of reliability risks and the opportunity to mitigate them early in the design process instead of after pre-development. Eliminating or minimizing the opportunity for mistakes to occur in manufacturing can be done early in the design process.

## 3.7.4 Limitations

Not intended for use in standard designs or processes.

#### 3.7.5 Estimated cost versus benefit

Cost includes risk of lower reliability if the models and simulations are wrong, computer and software overhead, time and cost needed to perform design of experiments, expertise in failure mechanisms. Benefits include a reduction in material needed for validation, faster cycle time, higher reliability if the models and simulation are right.

### 3.7.6 Defect type addressed (ongoing or spike)

Ongoing (controllable) and spike (extrinsic) defects.

# 3.7.7 Metrics used and meaning of values

Mean time to failure, warranty returns.

#### 3.7.8 References

JEP13A: Guideline for Constant Temperature Aging to Characterize Aluminum Interconnect Method for Stress Migration Induced Voiding

JEP119A: A Procedure For Executing SWEAT

JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments

JESD35: Procedure for Wafer Level Testing of Thin Dielectrics

http://www.npd-solutions.com/lifecycle.html

#### 3.7.9 Examples

- Design based on the expected range of the operating environment.

- Design to minimize or balance stresses and thermal loads and/or reduce sensitivity to these stresses or loads.

**Component Technical Committee**

- De-rate components for added margin.

- Provide subsystem redundancy.

- Use proven component parts & materials with well-characterized reliability.

- Reduce parts count & interconnections (and their failure opportunities).

- Improve process capabilities to deliver more reliable components and assemblies.

**Component Technical Committee**

#### 3.8 Simulation

#### 3.8.1 Description

Recreating the functioning of the component through computer modeling using established engineering and physics-based relationships to functionality, construction and reliability.

#### 3.8.2 Where this fits in the material flow

Performed on all components during the design phase and possibly during the evaluation phase. May be used during production to aid in debug or failure analysis (FA). Simulation should ALWAYS be used for every significant silicon pass.

## 3.8.3 Components and technologies this applies to and how it addresses zero defects

Verifies functional operation of the device in addition to highlighting process, voltage and temperature sensitivities related directly to the design and process parametrics.

#### 3.8.4 Limitations

Not intended for use after the component has been ramped up to full production (i.e., after initial release of the product). It may not always be needed in determining production yield issues or FA.

#### 3.8.5 Estimated cost versus benefit

Irrelevant during the design phase as it is impossible to design without simulation. May be slightly different if trying to use simulation as means to identify process or modeling issues. Cost includes running and analyzing data, and Q&R simulation program development/purchase. Benefit includes mitigating defects in design that otherwise would promulgate to manufacturing.

# 3.8.6 <u>Defect type addressed (ongoing or spike)</u>

Both ongoing and spike defects.

# 3.8.7 Metrics used and meaning of values

Direct simulation of specified parameters and functions. Parameter fit to empirical data, confidence bound.

# 3.8.8 References

JEP122B: Failure Mechanisms and Models for Silicon Semiconductor Devices

JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments

#### 3.8.9 Examples

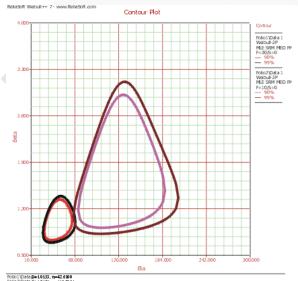

Example of a simulation is shown in figure 3.8a

**Component Technical Committee**

#### 3.9 Characterization

### 3.9.1 <u>Description</u>

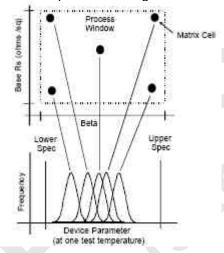

The process of collecting and analyzing data in order to understand the attributes, behavior and limitations of a process, product design and the package. The characterization is performed to generate the specification or datasheet for the product, process or package. Intent is to look at parametric performance of the device with temperature, voltage, frequency, etc. Characterized parts, generated either via corner lot processing or sorted as extreme parametric values, can then be applied to the application to determine sensitive process corners that the supplier can either shift or tighten the process away from or sort out at test.

# 3.9.2 Where this fits in the material flow

Typically performed on all new and changed components involving new designs or processes, at wafer probe or final test.

# 3.9.3 Components and technologies this applies to and how it addresses zero defects

Establishes the functional and parametric performance of the device by determining the electrical and process parametric and performance limits. The "sweet spot" of the process is then fed back into manufacturing where it can be controlled.

### 3.9.4 Limitations

Not intended for use after the component has been ramped up to full production (i.e., after initial release of the product).

# 3.9.5 <u>Estimated cost versus benefit</u>

Cost includes added testing for various parameters such as temperature, voltage, frequency, etc., and manufacturing corner lots varying parameters such as Vtn, Vtp, CD, Rs, etc.. Benefit includes centering of the process, test versus the intended application, and establishing more accurate process and test limits.

#### 3.9.6 Defect type addressed (ongoing or spike)

Ongoing.

## 3.9.7 Metrics used and meaning of values

Mean, minimum, maximum standard deviation, sample size, Cp, Cpk vs. datasheet or test limits, temperature, voltage, frequency, and process corner variables (e.g., Vt, Leff, Rs, CD). Determines capability.

# 3.9.8 References

AEC-Q003

AEC-Q100-009: Electrical Distribution Assessment

# 3.9.9 Examples

Example of a characterization is shown in figure 3.9a-d

**Component Technical Committee**

| COND. | PARAMETER | SPEC LO | SPEC HI  | AVG     | STD DEV | Ср    | Cpk   |

|-------|-----------|---------|----------|---------|---------|-------|-------|

| 1     | R1        | 3300.00 | 6100.00  | 4568.16 | 348.43  | 1.34  | 1.21  |

| 1     | R2        | 7000.00 | 13000.00 | 9488.32 | 744.22  | 1.34  | 1.11  |

| 1     | R3        | 1400.00 | 3200.00  | 2656.39 | 68.18   | 4.40  | 6.14  |

| 1     | R4        | 1400.00 | 3200.00  | 2626.69 | 55.62   | 5.39  | 7.35  |

| 1     | VOH       | 0.50    | 1.00     | 0.78    | 0.00    | 55.45 | 61.62 |

| 1     | VCEsat1   | 0.05    | 0.50     | 0.13    | 0.01    | 8.46  | 2.94  |

| 1     | VCEsat2   | 0.05    | 0.50     | 0.21    | 0.01    | 6.12  | 4.26  |

| 1     | VCEsat3   | 0.05    | 0.50     | 0.30    | 0.02    | 3.07  | 3.45  |

| 1     | Hfe       | 100.00  | 500.00   | 143.20  | 7.18    | 9.29  | 2.01  |

Golden unit comparison from one test location versus another

| <b>O O</b> 1 <b>G O</b> 1     | Jpa   | • •      |          |          |          |          |

|-------------------------------|-------|----------|----------|----------|----------|----------|

|                               |       | 3        | 2        | 4        | 5        | 6        |

| Search_Clock_Ed               | ns :  | 27.8     | 27.6     | 27.8     | 27.8     | 27.8     |

| iref_wh                       | uA    | 624,9359 | 631,7944 | 627,1404 | 629.1    | 523,7112 |

| RIDO_R                        | mΑ    | 29.6636  | 30.0302  | 29.7145  | 29.8316  | 29.2919  |

| ,0                            |       | (3       | 2        | - 4      | . 5      | 6        |

| Search_Clock_Ed               | ns    | 27.8     | 29       | 27.9     | 27,9     | 27.9     |

| iref vrh                      | uA    | 620.7493 | 628.4191 | 627.9874 | 632.3512 | 621.4826 |

| RIDO_R                        | mA:   | 29.5295  | 29.5295  | 30.1114  | 29.8496  | 29,1987  |

| ECOM - STWIKEN ALOOM! THEE! - | 1DAC  | 3        | 2        | -4       | - 5      | - 6      |

| Search_Clock_Ed               | nsins | 0.000%   | D.719%   | 0.360%   | 0.360%   | 0.350%   |

| iref_witi                     | uA/uA | 0.670%   | 0.534%   | 0.135%   | 0.517%   | 0.357%   |

| RIDO R                        | mA/mA | 0.452%   | 1.667%   | 1.336%   | 0.060%   | 0.318%   |

# Matrix Lot parameter range

# Schmoo plot

**Component Technical Committee**

#### 4. MANUFACTURING

# 4.1 Failure Mode and Effect Analysis (FMEA)

#### 4.1.1 Description

A process performed by subject experts that identifies potential failure modes and their effects on the system and customer, determines their severity, occurrence and detection, and identifies possible causes and controls. The FMEA document identifies the risks associated with something potentially going wrong (creating a defect - out of specification) in the production of the product. The FMEA identifies what controls are placed in the production process to catch any defects at various stages on the processing. This applies both to process and design (product) FMEAs.

#### 4.1.2 Where this fits in the material flow

Performed on all new components and systems before design of component or arrangement of process flow. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.

# 4.1.3 Components and technologies this applies to and how it addresses zero defects

Identifies all potential modes of failure in design and process, their risks and how to control them.

#### 4.1.4 Limitations

Not intended for use with a product that is fully mature or is entering obsoletion.

#### 4.1.5 <u>Estimated cost versus benefit</u>

Cost includes man-hours to generate the expert knowledge document and uncertainty to new unknown failure mechanisms/modes. Benefit includes prioritizing the circuit or process step most susceptible to part failure in order to improve it, and communicating learning throughout the organization.

#### 4.1.6 Defect type addressed (ongoing or spike)

Ongoing (controllable) and spike (extrinsic) defects.

# 4.1.7 Metrics used and meaning of values

Risk priority number (product of severity, occurrence and detection) used to pareto which failure mode or mechanism is most influential to product failure.

#### 4.1.8 References

FMEA-3: Potential Failure Modes & Effects Analysis, AIAG JEP131A: Process Failure Modes & Effects Analysis

## 4.1.9 Examples

Example of a FMEA is shown in figure 4.1a

| Process                       | www.nei                    | Or and the second                   |     | 0      | Potential                                                                         | Đ,   | Current -                                                     | Current                                            | D | 13  | l income i               | Wasterlines V                                 | Adds             | on Requit | 1     |     |     |

|-------------------------------|----------------------------|-------------------------------------|-----|--------|-----------------------------------------------------------------------------------|------|---------------------------------------------------------------|----------------------------------------------------|---|-----|--------------------------|-----------------------------------------------|------------------|-----------|-------|-----|-----|

| Function/<br>Regularisetts    | Patient<br>Patient<br>Mode | Potential<br>Effects) of<br>Pattern | 400 |        | Cristo)<br>Medicianos<br>d'Estre                                                  | 400- | Process<br>Controls<br>Revealor                               | Phoeses<br>Controls<br>Detection                   |   | 民庆姓 | Recurrences<br>Actionsis | Responsibility<br>& Target<br>Completion Date | Actions<br>Taken | 6 8 9     | 10.00 | 0.0 |     |

| Past - Pre & Past<br>burn-lis | Miching.                   | RA return / GA<br>rejects           |     | 200    | Devices<br>parened of<br>lest site,<br>context and<br>context shuffly             | 3    |                                                               | Hander hall, remove<br>and retool paramed<br>until | * | 72  | 401-1034-001-077         | PRODUCTION                                    | IMPLEMENTED      | *         | 40    |     | 22  |

|                               |                            |                                     |     | 100000 | Oray unix<br>letrounding<br>lander and<br>fature.                                 | 2    | Song any along units<br>found.                                |                                                    | 2 | 43  | 4331-904-001-077         | PRODUCTION                                    | IMPLEMENTED      |           | 24    | 40  | 10  |

|                               |                            |                                     | 1.  | 100    | Merginal<br>(Merces                                                               | 1    | Low year had be<br>along within the                           |                                                    |   | 10  | 401-004-001-077          | PE                                            | INPLEMENTED      | đ         | . 1   | 2   | 311 |

|                               |                            |                                     |     | 10     | Read report<br>Action / Read<br>Inny / Read<br>Accepted tray<br>and being<br>word |      | Stop texting I'no<br>'text' taken / Red<br>tray / Red sprayed |                                                    | + | 24  | 431+404-001-077          | PRODUCTOR                                     | INFLEMBITED      |           | 1     | 1   |     |

**Component Technical Committee**

# 4.2 Statistical Analysis of Variance

### 4.2.1 <u>Description</u>

Mathematical procedure for determining the variables in a process that most influences the output characteristics of a given product depending on the manufacturing parameters.

#### 4.2.2 Where this fits in the material flow

Applicable anywhere in the process flow where data is collected for variation analysis and design of experiments.

# 4.2.3 Components and technologies this applies to and how it addresses zero defects

Methodology whose results can better target the optimal parameters of a device or process in order to achieve optimum yield, function, and/or reliability.

#### 4.2.4 Limitations

Not intended for use with a product that is fully mature, is entering obsoletion, or if a failure never occurs.

## 4.2.5 Estimated cost versus benefit

Cost includes running the experiment and analyzing the data. Benefit includes improving the product and/or process via optimized process/product parameters.

# 4.2.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) defects.

#### 4.2.7 Metrics used and meaning of values

Degrees of freedom, confounding, aliasing, correlation coefficient, and variables.

#### 4.2.8 References

# 4.2.9 Examples

Example of A DOE is shown in figure 4.2a

**Component Technical Committee**

#### 4.3 Control Plan

#### 4.3.1 Description

A plan to control the product/process characteristics and the associated process variables to ensure capability (around the identified target or nominal) and stability of the product over time. For example, Cpk of critical characteristics of process measures stability over time.

#### 4.3.2 Where this fits in the material flow

Performed for all manufacturing processes after the design of component, arrangement of process flow, and completion of the FMEA. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.

## 4.3.3 Components and technologies this applies to and how it addresses zero defects

Identifies the monitors, tests and screens that measure the performance of the process in the manufacture of the product. Specifies control criteria (e.g., use of X-bar-R chart, how to set control limits).

#### 4.3.4 Limitations

None.

### 4.3.5 Estimated cost versus benefit

Cost includes man-hours to generate the document and translate the language across different locations. Benefit includes documenting the control monitors, methods of measurement, and test plans.

# 4.3.6 <u>Defect type addressed (ongoing or spike)</u>

Ongoing (controllable) and spike (extrinsic) defects.

# 4.3.7 Metrics used and meaning of values

Items to be recorded, observed, and measured, method of data analysis (e.g., Cpk, X-bar-R), equipment used for measurement/test, frequency of test, sample size, and datasheet or customer spec.

#### 4.3.8 References

APQP-2: Advanced Product Quality Planning & Control Plan

#### 4.3.9 Examples

Example of a control plan is shown in figure 4.3a

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                  | (See                                                          | -             | 19 9 |                                                      | - Heave                         |                                                       |                                         |                                                              |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 200 7 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------|---------------|------|------------------------------------------------------|---------------------------------|-------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Heren's | Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Patrick            | Product .                                                     |               | 307  | Production Pressure<br>District                      | Manager 1                       | tegis<br>les                                          | free.                                   | Committees (Co.)                                             | Bar Da          | Series<br>Ser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Frag. |

| TAPE &  | tios<br>raints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MILESCOTTON<br>MAN | Mind Arms<br>2 and<br>14 and<br>15 bend<br>15 bend<br>15 bend |               | 1    | Delived<br>Separate                                  | =                               | anni.                                                 | Armite.                                 | Videous shedi.<br>per maker                                  | esticator       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MAX.  |

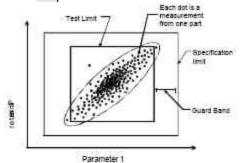

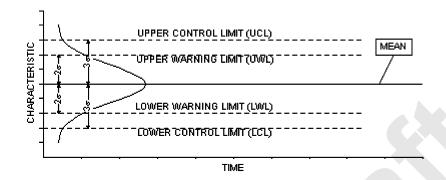

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | Parties                                                       |               | Dire | runu.                                                | ****                            | 1000                                                  | Service.                                | Common part<br>transparent<br>(Charles part<br>trappe (A.100 | RESILEPTED      | From State shows that the say |       |