Component Technical Committee

# GUIDELINES FOR STATISTICAL YIELD ANALYSIS

### **Automotive Electronics Council**

**Component Technical Committee**

### Acknowledgment

Any document involving a complex technology brings together <u>experience</u> and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the development <u>and release</u> of this document:

### Statistical Yield Analysis Sub-Committee Members:

Tim Haifley Altera

<u>Liam Ryan</u> <u>Analog Devices</u> <u>Xin Miao Zhao</u> <u>Cirrus Logic</u>

Roger TyldesleyCypress SemiconductorSteve BarlowDelphi CorporationJohn MonteiroDelphi Corporation

Paul GroschFreescaleNick LycoudesFreescaleLaurie McTurkFreescaleJames StanleyFreescaleAhmad Abde-YazdaniInfineonHorst LewitschnigInfineon

Gary FisherJohnson ControlsTom LawlerLattice Semiconductor

Harmeet SobtiMaximStefan EichenbergerNXPZhongning LiangNXP

Tony Walsh Renesas Electronics

Francis Classe Spansion

<u>Bassel Atallah</u> <u>STMicroelectronics</u> <u>Nga Nguyen</u> <u>Texas Instruments</u>

<u>Lee Simpson</u> <u>U.S. Army</u> <u>Cesar Avita</u> <u>Visteon</u>

### Automotive Electronics Council -

**Component Technical Committee**

### NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.

AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.

AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in conformance with this document shall be made unless all requirements stated in the document are met.

Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link http://www.aecouncil.com.

Published by the Automotive Electronics Council.

This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

Printed in the U.S.A. All rights reserved

Copyright © 2012 by the Automotive Electronics Council. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Technical Committee.

### Automotive Electronics Council —

**Component Technical Committee**

### **GUIDELINES FOR STATISTICAL YIELD ANALYSIS**

Text enhancements and <u>differences</u> made since the last revision of this document are shown as underlined text.

### 1. SCOPE

This guideline is intended for use as a method for detecting and removing abnormal lots of material and thus ensuring the quality and reliability of the ICs supplied as meeting AEC-Q100 or <u>AEC-Q101</u>. The principles described in this guideline are applicable to packaged or unpackaged die.

### 1.1 Purpose

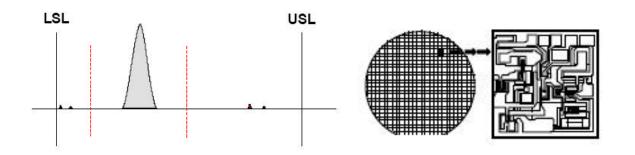

This guideline describes a method, utilizing statistical techniques <u>based on statistical yield limits</u> (SYL) and statistical bin limits (SBL) statistical computations, of identifying a wafer, wafer lot, or assembly lot that exhibits an unusually low yield or an unusually high bin failure rate. Experience has shown that wafer and assembly lots exhibiting these abnormal characteristics tend to have generally poor quality and can result in significant system reliability and quality problems.

The exact methods applied may vary from what is described in this guideline, specifically if distributions are non-normal. Such derived methods may be employed with good statistical justification. The supplier shall be prepared to justify the statistical approach used.

**Note:** For best SYL and SBL results, use test limits based on <u>Part Average Testing Limits</u> (PAT) as described in AEC Q001.

### 1.2 References

AEC-Q001 Guidelines for Part Average Testing

AEC-Q100 Stress Test Qualification for Integrated Circuits

AEC-Q101 Stress Test Qualification for Discrete Semiconductors

# 2. METHOD FOR ESTABLISHING STATISTICAL YIELD LIMITS (SYL) AND STATISTICAL BIN LIMITS (SBL)

### 2.1 Detailed Description for Basic Wafer / Wafer Lot / Assembly Lot Level Yield Limits

Collect data from at least six lots and characterize the nature of the statistical distribution for yield (good die per wafer) and for all critical fail bins, as determined between the supplier and user/customer (number of die failing for each fail bin cause). If the yield and fail bin distributions show a reasonable fit to a normal distribution (normal distribution is applicable), determine the mean and sigma value for the percentage of devices passing per lot and the percentage of devices failing each bin-out per lot (lot as used here could mean each wafer, a wafer lot or an assembly lot).

Early in production of a part, when data from six lots is not available, data from characterization/matrix lots, similar to existing products and design simulation, may be used to set preliminary limits. The preliminary limits shall be updated as soon as <u>current production data becomes</u> available. The review and update <u>should be performed periodically</u> using current production data during the first 6 months of production. This initial update exercise should be done with a frequency based on product ramp rate as is practical, such as after every 2 diffusion lots or every 30 days.

### Automotive Electronics Council =

**Component Technical Committee**

The current data used shall include the data available since the last update or at least the last 8 lots. Older data shall not be used. After the first 6 months of production the limits shall be updated at least twice per year or as agreed between supplier and user/customer. With this data determine the SYL and SBL (both on a wafer, wafer lot and assembly lot basis) as follows:

SYL1 = Mean - 3 Sigma SBL1 = Mean + 3 Sigma

SYL2 = Mean - 4 Sigma SBL2 = Mean + 4 Sigma

If the statistical distribution of good die per wafer or fail bin die/wafer does not fit a normal distribution, the supplier may use alternative methods. This may include transforming the data through mathematical manipulation so the normal distribution is applicable or fitting the data to another suitable distribution (Weibull, Gamma, Poisson, etc.) and establish SYL/SBL limits to achieve the same risk probabilities as one would achieve at 3s or 4s for a normal distribution. Any other method may be employed with good statistical justification. The supplier shall be prepared to justify the statistical approach used.

Any wafer or lots that fall below SYL1 or exceed SBL1 shall be <u>flagged</u> for engineering review. In addition, lots that fall below SYL2 or exceed SBL2 may be <u>quarantined</u>. <u>Supplier shall perform a risk assessment for disposition of quarantined material</u>. <u>Containment actions shall be taken to reduce risk to user/customer</u>. <u>Material below minimum yield threshold or with high reliability risk shall be scrapped</u>. For major excursions, supplier shall determine the root cause, corrective action, and future prevention. For any lots outside of the limits that will be shipped, notification per established agreement between supplier and user/customer shall be given.

### 2.2 Records

The supplier shall maintain records on all wafers, wafer lots and assembly lots that fall below  $\underline{SYL_2}$  or exceed  $\underline{SBL2}$ . This data shall include the root cause for the yield problem and corrective action taken to prevent reoccurrence of the problem. It should also include any special testing or screens that were performed on the wafer, wafer lot, or assembly lot and the customer that approved the shipment of the parts in question. The supplier shall apply their policy for records retention to these results.

### 3. CUSTOMER NOTIFICATION

### 3.1 Procedure for Customer Notification

Before the <u>user/</u>customer is notified, the supplier shall have determined the failure mechanism(s) and, based on his experience, determine the corrective action required to prevent a reoccurrence of the condition in future product. The supplier shall also present data on a reasonable expectation of the seriousness of the failure mechanism(s) and <u>its</u> impact on quality and reliability. Included in this data should be a plan for additional tests and screens which could provide the user/<u>customer</u> with reasonable certainty that the product he receives will be at least equal to normal product.

### 3.2 Procedure for Customer Notification Through Distribution Network

If the supplier <u>is unaware of</u> the <u>user/customer, in the case of the user/customer purchasing parts through distribution, then the supplier must maintain records of disposition for the lots falling below SYL<sub>2</sub> or exceeding SBL<sub>2</sub> that have been shipped to distributors. Any user/customer, purchasing through a distribution network, must understand that parts purchased from distribution may not meet AEC-Q002, unless prior agreement has been reached between supplier and user/customer.</u>

#

## **Revision History**

| Rev #    | Date of change       | Brief summary listing affected sections                                                                                                                                                                          |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -        | July 31, 1997        | Initial Release.                                                                                                                                                                                                 |

| Α        | Aug. 25, 2000        | Added Paragraph 1.2. Revised Paragraphs 1, 2.1, and 4.3.                                                                                                                                                         |

| <u>B</u> | <u>Jan. 12, 2012</u> | Complete Revision. Added Notice Statement. Revised (and renumbered where appropriate) Acknowledgement and Sections 1.1, 1.2, 3, 3.1, 3.2, 4, 4.1, and 4.3. Deleted signature block and Sections 2, 2.1, and 4.2. |